# 独创性声明

本人所呈交的学位论文是在导师指导下进行的研究工作及取得的成果。尽我所知, 除特别加以标注的地方外,论文中不包含其他人的研究成果。与我一同工作的同志对本 文的研究工作和成果的任何贡献均已在论文中作了明确的说明并已致谢。

本论文及其相关资料若有不实之处,由本人承担一切相关责任。

论文作者签名: ( 到 庆 2011年 4 月 1 日

# 学位论文使用授权

本人作为学位论文作者了解并愿意遵守学校有关保留、使用学位论文的规定,即:在导师的指导下创作完成的学位论文的知识产权归西安理工大学所有,本人今后在使用或发表该论文涉及的研究内容时,会注明西安理工大学。西安理工大学拥有学位论文的如下使用权,包括:学校可以保存学位论文;可以采用影印、缩印或其他复制手段保存论文;可以查阅或借阅。本人授权西安理工大学对学位论文全部内容编入公开的数据库进行检索。本学位论文全部或部分内容的公布(包括刊登)授权西安理工大学研究生学院办理。

经过学校保密办公室确定密级的涉密学位论文,按照相关保密规定执行;需要进行技术保密的学位论文,按照《西安理工大学学位论文技术保密申请表》内容进行保密(附《西安理工大学学位论文技术保密申请表》)。

保密的学位论文在解密后,适用本授权。

论文题目:基于嵌入式技术的激光雷达高速数据采集系统关键技术研究

学科名称: 测试计量技术及仪器

研究生: 闫庆

指导教师: 华灯鑫 教授

签名: 数据: 数据:

摘要

激光雷达作为一种全新的探测技术,因其具有较高的时空分辨率和测量精度,而广泛应用于大气参数探测、污染物监测、沙尘暴监测等领域。激光雷达的回波信号涵盖了大量的信息,研制具有高速、高精度的数据采集系统,对提升激光雷达系统的整体性能有着十分重要的作用及意义。

本文依托西安理工大学激光雷达遥测研究中心试验平台,在充分分析激光雷达的探测原理及其回波信号的特点的基础上,设计了一套基于嵌入式技术的用于激光雷达模拟探测的双通道高速数据采集系统。系统采样率为 20MSPS,设计分辨率为 14 位。针对激光雷达回波信号的特点,系统总体设计采用在板存储器方式进行数据传输和采集,采用外部信号触发的方式启动数据采集,数据存储的同时进行必要的数字信号处理。

本文重点研究分析了系统的设计原理、硬件结构和软件流程。采用 Atmel 公司 AT91SAM9260 处理器作为数据处理器件,Altera 公司 CPLD 芯片 EPM7032AE 作为时序逻辑产生器件,AD 公司的双通道模数转换器件 AD9248 作为数据采集器件,以及 IDT 公司生产的 FIFO 芯片 IDT72V233 作为数据缓存器件,构建了系统的硬件结构,并对各模块详细阐述了设计思路和关键技术及其解决方法。在 Quartus II 平台下结合 Verilog 语言,编写了该系统的时序逻辑产生程序。利用米散射激光雷达实验原始数据,研究并分析了回波信号信噪比的改善方法,提出了算术平均作为该系统的数据预处理方式。在此基础上,论文也设计了一种利用 FPGA 代替 CPLD 和 FIFO 的系统改进方案。

本文设计方案为激光雷达采集技术的发展提供了一种设计思路,对于其他不同类型的激光雷达具有通用性和参考性。

**关键词:** 激光雷达; 数据采集; ARM; CPLD

本论文研究工作得到国家重大基础研究计划 (973 计划, No. 2009CB426302)、国家自 然科学基金 (No. 40675015)

# Title: RESEARCH ON KEY TECHNIQUES OF THE HIGH SPEED EMBEDDED DATA ACQUISITION SYSTEM FOR LIDAR

Major: Technology & Instrumentation of Testing and Measuring

Name: Qing YAN

Supervisor: Prof.Dengxin HUA

Signature: Dayson Hold

## **Abstract**

Because of high spatial and temporal resolution and measurement accuracy, lidar, as a new detection technology, is widely applied in the atmospheric parameters detection, pollutant and dust storms monitoring and so on. Since lidar echo signals carry a great deal of information, it has important function and significance for promoting the performance of system to develop data acquisition systems for lidar echo signals with high speed and high accuracy.

Relying on lidar remote sensing Research Center test platform of Xi'an University of Technology, based on completely analysing the dectetion principle of lidar and the characteristic of echo signals, a dual-channel high-speed data acquisition system for lidar simulation detection is designed based on embedded technology with the sample rate of 20 MSPS and design resolution of 14 bit. According to the feature of echo signals, the on-board RAM for data transmission and collection are adopted, which sets the cache device on circuit board. Also, data collection of the system should be triggered by external signals, and when the data storage process starts, the necessary digital signal should be processed simultaneously.

In this thesis, the design principle, hardware structure, and software process of the system are mainly discussed. With AT91SAM9260 processor of Atmel Company as the data processing device, CPLD chips EPM7032AE of the Altera company as a sequential logic device, dual-channel ADC device AD9248 of AD company as data collection device, and FIFO chip IDT72V233 of IDT company as data caching device, the hardware structures of this system are built. The detailed design ideas, problems encountered and solutions are discussed in different modules. Based on the Quartus II platform, combining Verilog language, the generated sequential logic programs of the system are designed and timing simulation is processed. By utilizing the raw data of Mie scattering lidar experiment, analyzing the method of improving the signal-to-ratio of echo signals, the arithmetic average measurement is selected as data preprocessing method for the system. Also, a modified program by replacing FPGA with CPLD

and FIFO devices is provided.

This design provides a new idea for development of lidar data acquisition technique and it is also applicable for other different types of lidar system.

Keyword: Lidar; Data Acquisition; ARM; CPLD

This work was supported by National Basic Research Program (973 Program, No.2009CB426302), National Science Foundation (No.40675015).

# 目录

| 1 | 绪论      |                      |

|---|---------|----------------------|

|   | 1.1 课题  | 的背景及意义1              |

|   | 1.2 国内  | 外研究现状 2              |

|   | 1.3 论文  | 的主要研究工作4             |

|   | 1.4 本章  | 小结4                  |

| 2 | 激光雷达数   | 据采集系统总体设计方案5         |

|   | 2.1 激光  | 雷达数据采集系统设计基础5        |

|   | 2.1.1   | 激光雷达工作原理及系统结构5       |

|   | 2.1.2   | 激光雷达信号特点分析6          |

|   | 2.2 激光  | 雷达数据采集系统总体设计方案8      |

|   | 2. 2. 1 | 激光雷达数据采集系统设计要求8      |

|   | 2. 2. 2 | 激光雷达数据采集系统总体设计方案8    |

|   | 2.3 本章  | 小结12                 |

| 3 | 激光雷达数   | 据采集系统硬件设计13          |

|   | 3.1 激光  | 雷达采集系统硬件设计总体架构13     |

|   | 3.2 激光  | 雷达数据采集系统各模块功能和硬件实现14 |

|   | 3. 2. 1 | 模拟通道模块设计14           |

|   | 3. 2. 2 | 数据采样模块设计16           |

|   | 3. 2. 3 | 时序控制模块设计19           |

|   | 3. 2. 4 | 数据缓存模块设计 23          |

|   | 3. 2. 5 | 数据处理模块设计 26          |

|   | 3. 2. 6 | 电源模块设计 30            |

|   | 3.3 激光  | 雷达数据采集系统硬件抗干扰性设计31   |

|   | 3.4 本章  | 小结 32                |

| 4 |         | 居采集系统软件设计33          |

|   | 4.1 激光  | 雷达采集系统数据采集程序设计35     |

|   | 4. 1. 1 | AD 采集程序设计35          |

|   | 4. 1. 2 | FIFO 缓存程序设计37        |

|   | 4.2 激光  | 雷达采集系统数据处理程序设计38     |

|   | 4. 2. 1 | 数据预处理方法分析 38         |

|   | 4. 2. 2 | 10                   |

|   |         | 小结45                 |

| 5 | 激光雷达数据  | 居采集系统的改进与优化46        |

### 西安理工大学硕士学位论文

| 5.1 方案改进与优化      | . 46 |

|------------------|------|

| 5.2 改进方案的实现      | . 46 |

| 5.2.1 FIFO 存储器设计 | . 46 |

| 5.2.2 电源设计       | . 48 |

| 5.3 本章小结         | . 50 |

| 6 总结与展望          |      |

| 6.1 总结           | . 51 |

| 6.2 展望           |      |

| 致谢               | . 53 |

| 参考文献             | . 55 |

| 附录 A             | . 57 |

| 附录 B             |      |

| 攻读硕士期间发表的论文      |      |

|                  |      |

## 1 绪论

## 1.1 课题的背景及意义

激光雷达是一种近几十年发展起来的新的探测技术,由于其具有高时空分辨率及高探测灵敏度等优点,被广泛的应用于大气、海洋、陆地和其他目标的遥感探测中<sup>[1]</sup>。

通常认为用于大气探测的激光雷达主要由三大部分组成。包括激光发射系统(例如激光器、准直扩束系统等)、光学接收系统(例如望远镜、分光系统等)和数据采集及控制系统(例如数据采集卡、光子计数器、示波器等)。显而易见数据采集系统是激光雷达系统的重要组成部分,其功能的好坏直接决定着整个激光雷达系统的优劣<sup>[1, 2]</sup>。

在激光雷达大气探测过程中,不仅要探测位置信息,更主要是得到回波信号的强度信息,因为对诸如大气温度、大气水汽含量、大气消光系数、大气气溶胶浓度以及大气风速等大气物理参数的反演都是基于激光雷达回波信号的强度。由于激光雷达探测到的大气回波信号是以距离平方衰减,其回波信号的动态范围较大,数据分析工作量大,需要重视强背景光下的小信号提取技术。另外,要使激光雷达获得较高的空间分辨率,则必须对数据进行高速高精度采样。同时,由于激光雷达系统本身及环境因素的影响,回波信号存在粗大误差和系统误差,单次回波信号并不能准确的反映大气特征,需要使用多组数据的平均值作为测量结果。由此可见,高速高精度的数据采集系统直接决定了后期物理意义的探讨与研究的准确度。

目前市场所售的高速数据采集卡(器)大部分不是针对激光雷达系统研制开发的,一般情况其只有普通的数据采集功能。虽然在采样率和分辨率上已经满足了激光雷达的使用要求,但是硬件连续触发、多组采集平均等功能都不具备,使用时需要通过上位机系统提供触发信号开启系统采集功能,采集过程中存在脉冲遗漏现象且很难保证实时性。另外,数据采集卡不是自主研发,核心技术和硬件底层不对用户开放,使用时需要遵循原设计者的设计思路,与激光雷达系统不能完全匹配,开发利用很不方便。现有的普通示波器在数据采集过程中同样存在脉冲遗漏现象,且使用起来很不方便,数据不能与PC 机直接连接,需要使用移动存储设备过渡,不能及时的反演大气特征信息。部分高端数字示波器能满足大动态范围的实时大数据量采集,但是其价格昂贵,携带性差,阻碍了激光雷达产品化进程。

部分激光雷达研究机构选用的 PCI 插槽方式的数据采集卡安装麻烦,受计算机插槽数量、地址、中断资源限制可扩张性差,在一些电磁干扰强的测试现场,无法专门对其做电磁屏蔽,导致采集的数据失真。还有一些激光雷达研究机构致力于自己开发数据的采集系统,但其使用单片机作为主控单元,控制 AD 及外围芯片的工作,但因其时钟频率低,无法满足现有的高速数据采集的要求导致数据失真<sup>[3]</sup>。

综上所述,设计具有较高采样速率和高数据量化位数且成本不高的激光雷达专用数据 采集系统可以为激光雷达系统提供技术支持,提高激光雷达的整体性能,改善大气参数探 测的信噪比,获得更为准确的大气信息,降低整个激光雷达系统的成本,保证了激光雷达系统的知识产权。

## 1.2 国内外研究现状

从 1963 年,激光雷达研制成功并用于大气探测开始,其种类日益呈现多样化:包括米散射型激光雷达发展为多普勒激光雷达,拉曼激光雷达,差分吸收激光雷达,共振激光雷达,偏振激光雷达等多种激光雷达;激光雷达的激光波长也由单一波长发展到多波长;其形式也由地基激光雷达发展为车载式、机载式、球载式和星载式激光雷达<sup>[3]</sup>。虽然激光雷达的类型繁多,结构差异很大,但是所有的激光雷达都不可避免的涉及到激光雷达回波信号的采集问题。关于如何提高其测量精度、空间分辨率等问题一直是国内外激光雷达研究人员致力于解决的问题。数据采集系统作为激光雷达重要组成部分,也不可或缺的成为大家关注研究的对象<sup>[3-6]</sup>。

通常情况下,激光雷达的数据采集方式分为光子计数方式,模拟探测方式以及光子计数和模拟探测相结合的方式。光子计数方式主要针对激光雷达信号呈现出随着时间离散分布的光脉冲信号,例如高空探测或者回波效率低的低空探测。对于这种方式,一般采用光子计数器或者光子计数采集卡,如图 1-1 所示为 SR400 型光子计数器实物图。模拟探测方式主要针对激光雷达信号呈现具有一定幅值的电压随时间变化的模拟信号,例如低空探测。对于这种方式,一般采用示波器或者数据采集卡,如图 1-2 所示为泰克示波器实物图。光子计数和模拟探测相结合的方式,是一种比较理想的方式,低空探测可以采用模拟探测方式,高空探测采用光子计数方式,这样可以进行更远距离的探测,提高激光雷达的整体性能<sup>[7]</sup>。

图 1-1 光子计数器实物图 Fig. 1-1 the picture of photon counter

图 1-2 示波器实物图 Fig. 1-2 the picture of oscilloscope

模拟探测使用的示波器以及光子计数探测使用的光子计数器携带不方便,而且示波器单一数据的平均方式影响最终平均数据的结果和准确性。相比之下,数据采集卡使用起来较为方便,国内外激光雷达研究机构都将选用和设计数据采集卡作为激光雷达研究的一项重要任务。

一些研究机构采用现成的数据采集卡,通过要求原设计者进行技术改良来满足激光雷达的使用要求。其中安徽光机所大气光学中心研制的 AML-1 激光雷达系统,采用了分辨率 12 位,采样率 40MSPS 的成都纵横测控技术公司的 JV52014 数据采集卡。该中心研制的 ATS-1 激光雷达系统,使用计数频率 150MSPS 的 AMETEK 公司的 MCS-PCI 光子计数卡以及分辨率 16 位,采样率 10MSPS 的 Gage 公司的 CS1610 数据采集卡<sup>[7]</sup>。西安理工大学激光雷达遥测研究中心研制的微脉冲米散射激光雷达系统,采用了分辨率 16 位,采样率 20MSPS 的凌华公司的 PCI-9826 数据采集卡<sup>[8]</sup>。

另外一些研究机构寻求自主设计和研发应用于激光雷达系统的数据采集卡。其中武汉大学设计了分辨率为 8 位,采样率 200MHz 的用于瑞利和钠共振荧光激光雷达的数据采集系统,用于研究中纬度地区钠层的结构及长期变化。该系统主要以 FPGA 为主控单元,AD9054 为模数转换器件,USB 总线作为系统与 PC 机的数据传输接口<sup>[9]</sup>。西安电子科技大学采用 FPGA 结合 DSP 的方式研制了相关采集卡,在理论探讨和仿真阶段已经有了初步的成果<sup>[10]</sup>。中国海洋大学使用 FPGA 作为主控单元,正在研制具有两通道模拟探测和 6 通道光子计数探测的激光雷达数据采集系统。

图 1-3 licel 激光雷达数据采集系统实物图 Fig. 1-3 the picture of data acquisition of licel

1994年 Dr. Bernhard Stein and Bernd Mielke 建立 Licel 公司,1996年该公司在柏林正式创立。该公司名称 Licel 的全称是 Lidar computing and electronics。其生产的产品主要是应用于激光雷达探测的光子计数探测方式与模拟探测方式相结合的数据采集系统,图 1-3 所示为 licel 公司数据采集系统的的实物图。该公司 2010年 12 月最新研制成功的数据采集系统具有 16 位分辨率,20MSPS 采样率的模拟探测功能以及 250MHz 的光子计数功能,

其目前售价为 9100 欧元。一般情况单纯购买仅有采集功能的 licel 不能满足探测要求,需要再配置 PMT 等附属设备,因此构建一套激光雷达专用的完整数据采集系统需要人民币 40 万左右,成本比较高[11]。

## 1.3 论文的主要研究工作

本文将以六个章节给出应用于激光雷达数据采集处理的 14 位、20MSPS 双通道数据 采集系统。分析了该系统的工作原理,设计了硬件结构,编写了软件程序。以微脉冲米散 射激光雷达为例,分析了各种数据处理方法的特点,通过反演每种方法的距离平方校正信 号,提出算术平均作为反演前期的数据预处理方式。在此基础上,对系统设计方案进行了 改进。各章节的具体内容如下:

第一章:阐述了本课题的研究背景及研究意义。通过分析现有激光雷达数据采集系统的研究现状,明确了自主开发激光雷达数据采集系统的必要性和现实意义。

第二章:设计了激光雷达数据采集系统的总体方案。在分析激光雷达探测原理和系统 结构的基础上,明确了激光雷达的数据特点,设计了激光雷达数据采集系统的总体方案。

第三章:设计了激光雷达数据采集系统的硬件结构。根据系统总体设计方案,设计了激光雷达数据采集系统的硬件结构,按照模块化思想对于系统的每个重要部分做了详细的设计,对设计中的难点以及需要注意的问题给予了详细的分析说明。

第四章:设计了激光雷达数据采集系统的软件。根据激光雷达采集系统的硬件结构和主要功能编写了系统的软件程序,主要包括时序控制部分和数据处理部分。对采集系统中的程序设计流程给予了详细的说明,针对每个模块的程序编写进行了详细的讨论,并且提供了部分关键性程序的代码。以微脉冲米散射激光雷达实验原始数据为例,分析了各种平均方法的优劣,利用每种平均方法获得的结果反演了激光雷达距离平方校正信号,并提出了算术平均作为反演前期的在板数据预处理方式。

第五章:设计了系统的改进方案。根据前期设计过程中存在的问题,设计了激光雷达数据采集系统的改进方案,并就相关技术进行分析、探讨。

第六章: 总结与展望。对全文工作进行了总结,对下一步的工作进行了分析和展望。

## 1.4 本章小结

本章主要介绍了激光雷达数据采集系统在整个激光雷达大气探测中的关键作用,详尽的对比了中外在该领域的研究成果以及存在的问题。分章节阐述了本论文的主要研究内容,进而明确了开发高速高精度数据采集系统对于推动激光雷达的发展以及提高激光雷达探测精度的重要性。

# 2 激光雷达数据采集系统总体设计方案

激光雷达数据采集系统主要应用于激光雷达回波信号的采集,该信号特点有别于其他测量系统产生的信号,所以在提出设计方案之前有必要分析激光雷达的工作原理和系统结构,直观的了解激光雷达回波信号的特点,从而提出该系统的设计要求,并且根据这些要求提出激光雷达数据采集系统的总体设计方案。

## 2.1 激光雷达数据采集系统设计基础

#### 2.1.1 激光雷达工作原理及系统结构

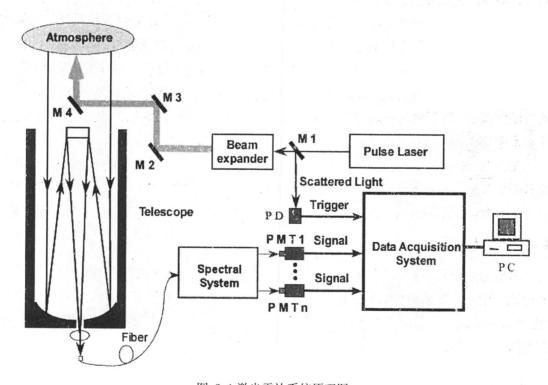

激光雷达作为一种主动式大气测量系统,其系统原理图如图 2-1 所示。将脉冲激光经过分束镜 M1 变为两路:一路经过 PD 转变为电信号,作为数据采集系统的外部触发信号;另外一路通过准直扩束系统后,再经过 M2-M4 三个反射镜保持与望远镜同轴的方式入射到大气中,激光与大气中的物质发生相互作用,利用望远镜接收散射的激光回波信号,通过光纤传输进入分光系统,根据探测的物质不同,分光产生的信号也不同,每一路光信号都通过一个 PMT 转变为电信号,利用数据采集系统完成电信号的采集,并且送到 PC 机进行数据分析、反演。

图 2-1 激光雷达系统原理图 Fig 2-1 Schematic diagram of lidar system.

该系统接收到的位于距离 r 处的散射回波信号强度 P(r)由激光雷达方程决定。如公式 (2.1) 所示。

$$P(r) = K \cdot E_0 \cdot \frac{c \cdot \tau}{2} \cdot \frac{A_r}{r^2} \cdot Y(r) \cdot \beta(r) \cdot \exp\left[-2\int_0^r \sigma(r) dr\right]$$

(2.1)

式中,K 表示系统常数; $E_0$  表示发射的激光脉冲能量(单位:J); c 表示光速(单位:m/s);  $\tau$  表示激光脉冲间隔时间(单位:s); $A_r$  表示望远镜有效接收面积(单位: $m^2$ );Y(r)表示发射和接收光束重叠的几何因子; $\beta(r)$ 表示距离 r 处大气的后向散射系数(单位: $sr^{-1}m^{-1}$ );  $\sigma(r)$ 表示距离 r 处的大气消光系数(单位: $m^{-1}$ )。

## 2.1.2 激光雷达信号特点分析

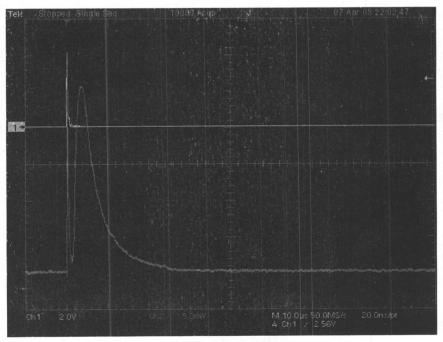

由激光雷达系统原理图 2-1 可知激光雷达系统的激光器和光电转换器件为数据采集系统提供了2类输入信号: 触发信号和回波信号。以西安理工大学激光雷达遥测研究中心日常开展的激光雷达实验为例: 探测气溶胶实验产生一路回波信号, 探测温度实验产生两路回波信号, 探测水汽实验产生三路回波信号。图 2-2 所示为示波器采集到的米散射激光雷达系统探测气溶胶实验时的实测波形图。其中一通道所示为触发信号, 二通道所示为回波信号。

图 2-2 米散射激光雷达系统实验波形图 Fig 2-2 Experimental oscillogram of Mie scattering lidar system

触发信号是由 PD 接收激光器发射时的杂散光转换而来,其频率与脉冲激光器发射的激光频率一致,且没有经过大气物质的相互作用,其波形、脉冲宽度与幅值变化不大,幅

值范围在 0-5V 之间,可以通过 PMT 输出端的流压转换电路将信号调整到采集系统触发端可以接收的范围。触发信号不仅是整个数据采集系统的时间基准,保证采样数据的同步性,避免数据的冗余。更重要的是触发信号还是后期数据反演的基准,在反演大气参数高度分布图时,以接收触发信号的时间点采集到的回波信号数据作为探测高度起始位置。

回波信号是由 PMT 接收到的经过和大气物质相互作用后的激光雷达散射信号,其脉冲宽度与幅值根据大气环境的变化而变化,动态范围较大。回波信号涵盖了大气参数信息,是数据采集系统主要采集的信号。该信号与其他测量系统得到的信号相比,有着独有的特点:

- (1) 由激光雷达方程(2.1) 可知,激光雷达回波信号受到大气消光系数及后向散射系数的影响,属于微弱信号。激光雷达实验需要采集回波信号的波形电压幅度数据,测量得到单次回波信号存在着大量的粗差和系统误差,不能准确的反映大气特征,需要采用多组数据的平均值作为测量结果,因此激光雷达数据采集系统的实时数据量相当大。以西安理工大学激光雷达遥测研究中心的激光雷达系统为例:实验过程中需要采集数据 10000组,每组 2000 个点,数据量可以达到 2×10<sup>7</sup>个,如果每个数据按照 2Bytes 计算,则数据量将近 40MB。

- (2)激光雷达回波信号以光速传播,因此具有时空分布特性。如果知道数据点对应的采样时间,再结合该点大气参数信息就可以绘制出大气参数信息的高度分布情况。为了准确的表达大气特征信息,需要激光雷达具有较高的空间分辨率(定义空间分辨率用 M 表示,其单位为 m)。公式(2.2)到公式(2.5)所示为激光雷达空间分辨率的数学关系式(仅仅考虑数据采集系统对激光雷达系统空间分辨率的影响)。其中 R 表示探测距离(单位: m); c 为光速; t 表示采样时间(单位: s); f s 表示采集系统采样频率(单位: SPS); T 表示采集单个数据的周期(单位: s); n 表示单次触发采集的数据点数。根据公式,通常情况以 20MSPS 采样率采集数据,则采集单次单个数据周期为 50ns,一次触发采集100us,则单次数据为 2000 个,可以探测的距离为 15km,空间分辨率可以达到 7.5m。由此可知,提高采样率有助于提高激光雷达的空间分辨率。

$$R = \frac{c * t}{2} \tag{2.2}$$

$$f_{-s} = \frac{1}{T} \tag{2.3}$$

$$t = T * n \tag{2.4}$$

$$M = \frac{R}{n} = \frac{\frac{c*t}{2}}{\frac{t}{T}} = \frac{c*T}{2} = \frac{c*\frac{1}{f\_s}}{2} = \frac{1}{2}*\frac{c}{f\_s}$$

(2.5)

## 2.2 激光雷达数据采集系统总体设计方案

## 2.2.1 激光雷达数据采集系统设计要求

根据激光雷达工作原理以及回波信号特点,激光雷达数据采集系统需要满足以下几点要求:

- (a) 具有高速,高分辨率采样能力。通常情况 12bit-14bit 分辨率,20MSPS-50MSPS 采样率可以满足激光雷达数据采集要求。

- (b) 具有硬件连续触发功能。系统接收到外部触发后,可以连续采集数据 2000-5000 次。要求系统具有时序控制单元,而不是通过上位机提供时序逻辑,应该采用硬件实时触发。

- (c) 具有数据处理功能。采集到的数据能够实现不同间隔期相同采样序列的数据累加,达到单组采集要求后,进行平均处理。

- (d) 具有大存储空间。由分析可知,激光雷达进行大气探测时产生的数据量大,需要采集系统具有较大的存储空间,采集到的激光雷达信号数据先存储在采集系统上,采集结束后送入上位机或者移动设备用于数据反演。

- (e) 具有多采集通道。激光雷达进行大气探测时,通常回波信号经过分光系统后会产生多路信号,要求数据采集系统应该能够具有多路采集功能,且需要保证多路信号的同步性。

# 2.2.2 激光雷达数据采集系统总体设计方案

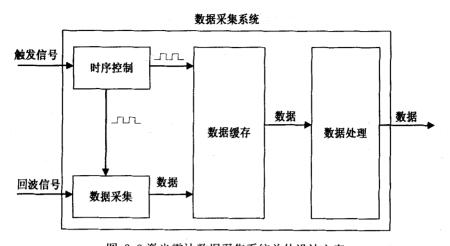

现如今,随着电子技术的迅速发展以及计算机在自动检测和控制中的广泛应用,越来越多的地方利用数字系统来处理模拟信号。对于高速数据的采集,需要将数据采集部分采样数据同步读出。如果采用模数转换器件与核心处理单元直接连接的方式进行数据采集,一般的核心处理单元速度不够且容易造成数据的丢失。为了避免这一问题的产生,做到数据采集部分和数据处理部分在时间上的相对独立,本设计总体采用在板存储器方式进行数据传输和采集,此方式主要是在采集系统中设计一个高速缓冲器件,将模数转换器件的转换结果先由硬件以高速写入缓存器中,然后由核心处理单元读出进行数据预处理,再传送到主存储器件中。其系统设计方案如图 2-3 所示。

设计的激光雷达数据采集系统主要由时序控制、数据采集、数据缓存和数据处理四个主要部分组成。系统需要以触发信号为时间基准,控制系统采集启停,在系统上电开始工作时不需要等待上位机提供时钟信号,而由硬件本身提供一个连续的时钟信号,避免由于操作系统的响应时间问题导致数据丢失。当数据达到事先设定好的数据上限后,统一上传到上位机。

对于一个数据采集系统而言,数据采集部分通常使用模数转换器件,在本文中就不详细论证了,而其他部分的选择范围比较大,所以接下来针对总体设计方案中设计的时序控

制部分、数据缓存部分和数据处理部分进行具体的选择论证。

图 2-3 激光雷达数据采集系统总体设计方案

Fig. 2-3 Overall design scheme of lidar data collection system

#### (1) 时序控制单元的选择

该系统要求接收外部触发信号后由时序控制单元连续产生满足要求的采样时钟信号。通常情况下,时钟信号的产生主要采用固定频率的晶振提供固定采样频率,也可以利用 CPLD/FPGA 器件构建时序逻辑电路。表 2-1 所示为 CPLD/FPGA 器件与晶振的比较表。

| Tab. 2-1 Common method comparison of selection   是否需   名称     功耗 操作方便   编程 |    |     |     | tial logic pi<br>精度 | roducing<br>其他功能 |

|----------------------------------------------------------------------------|----|-----|-----|---------------------|------------------|

| CPLD<br>FPGA                                                               | 较高 | 较复杂 | 是   | 好                   | 有                |

| 晶振                                                                         | 一般 | 简单  | 不需要 | 好                   | 无                |

表 2-1 常用产生时序逻辑的方法比较

由表 2-1 可知,两种实现方法都可以提供系统的时序逻辑。相比采用固定频率晶振而言 CPLD/FPGA 有以下两个突出优点:

- (a) 单一芯片可以容纳逻辑门数到上百万门,实现的功能也越来越强。特别是具有逻辑功能:例如产生逻辑时序、控制信号、设置存储器等,高端 FPGA 还可以植入软核,作为微处理器使用。

- (b) 用户可以反复地编程、擦除、使用或者在外围电路不动的情况下,利用不同软件实现不同的功能。

根据激光雷达设计要求,在进行激光雷达实验探测不同大气参数的时候,需要使用不同的采样频率,要求该系统可以设置不同的采样频率。因此在本设计中,需要使用可以产生时序逻辑的器件。另外,采集系统需要对其它器件的功能管脚进行逻辑控制,所以在本系统的设计中主要采用 CPLD/FPGA 构建时序逻辑电路,实现控制、数据传送的同步进行。为了保证系统可以提供连续的时钟信号,设计的时候在时序部分多设计一个满足采样要求的产生固定时钟频率的晶振,使得在后续的调试实验中确保采集数据过程的万无一失。

#### (2) 数据缓存单元的选择

该系统需要多处理器分工完成信号采集,由于激光雷达数据包含着时间信息,系统对时间的要求非常苛刻,直接使用高速器件采样有可能造成数据丢失。根据总体设计要求,采用在板存储器方式。该方式是在 AD 器件后面设置一个快进慢出的 RAM。AD 转换结果以规定采样速度高速写入该器件,而后主机再读出。通常使用 RAM 随机存储器作为缓存单元。表 2-2 所示为可以作为存储单元的 RAM 主要类型。

表 2-2 存储单元分类

Tab. 2-2 Classification of Storage unit

单端口存储器 多端口存储器

SRAM(静态 RAM) 双口 RAM

DRAM(动态 RAM) FIFO

单端口存储器中常用的器件为 SRAM 和 DRAM 两种。SRAM 优点是速度快,不必配合内存刷新电路,缺点是集成度低、功耗大,相同的容量体积较大,价格高,只能将数据保持很短的时间。DRAM 为了保持数据,使用电容存储,所以必须隔一段时间刷新一次,如果存储单元没有被刷新,存储的信息就会丢失。由于该系统设计中,缓存单元写入时间要快于读出时间,所以如果采用单端口的存储器,在软件编写上非常麻烦,且不能达到一边采集一边读取的要求,故采用多端口存储器的方式更适合激光雷达数据采集系统。

多端口存储器中常用的器件是双口 RAM 和 FIFO。双口 RAM 最大的特点是存储数据共享,一个存储器配备两套独立的地址、数据和控制线,允许两个独立的 CPU 或控制器同时异步地访问存储单元。FIFO 最大的特点是先进先出只允许两端一个写,一个读,因此 FIFO 是一种半共享式存储器。在双机系统中,只允许一个 CPU 往 FIFO 写数据,另一个 CPU 从 FIFO 读数据。而且,只要注意标志输出,空指示不写,满指示不读,就不会发生写入数据丢失和读出数据无效的状况。

表 2-3 所示为多端口存储器中常见的双口 RAM 和 FIFO 的特点分析。双口 RAM 在

仲裁控制方面比 FIFO 要复杂,容量比 FIFO 大。FIFO 操作简单,只给外部提供一个读信号和一个写信号,因此 CPU 用一个 I/O 地址便可读或写 FIFO,使硬件趋于简单,给编程也带来一些方便,但 CPU 不能对 FIFO 内部的存储器进行寻址。双口 RAM 由于有两套地址线,使硬件较 FIFO 复杂,但允许 CPU 访问内部存储单元,因此 CPU 之间可以自己分配数据块以及数据单元,使软件设计更加灵活。

表 2-3 FIFO 与双端口 RAM 比较

| Tab 2.3  | Comparison | hatwaan | FIFO and | dual-part RAM   |

|----------|------------|---------|----------|-----------------|

| 120. 2-3 | Comparison | Detween | riro and | uuai-pari Kaivi |

| 名称        | 仲裁控制 | 容量 | 硬件 | 软件  | 是否可<br>以寻址 |

|-----------|------|----|----|-----|------------|

| 双口<br>RAM | 复杂   | 大  | 复杂 | 灵活  | 可以         |

| FIFO      | 简单   | 小  | 简单 | 较灵活 | 不可以        |

由表 2-3 可知,如果单纯从使用角度判断,双口 RAM 操作更方便,可以通过寻址找到需要的数据。但是同样位数的双端口 RAM 比 FIFO 多两套地址线,读取数据的同时还需要操作地址,容易造成误读,给采集系统软件带来麻烦,容易造成数据的混乱和丢失。而且高速数据采集系统中减少芯片的端口,可以减少连接线和降低 PCB 板布线中的干扰问题。所以本设计选择 FIFO 作为数据采集系统的缓存单元。

#### (3) 数据处理单元的选择

该采集系统中数据处理单元的主要作用是将激光雷达采集到的多组数据进行数据预处理,所以需要核心器件具有存储量大,外设丰富且运算能力强的特点。常用的可以作为核心处理器件的芯片主要有单片机,DSP 以及 ARM。表 2-4 所示为三种常用处理器件的性能比较。

表 2-4 常用处理芯片比较

Tab. 2-4 Comparison of common processing chip

|     |                       | <u>^</u>                              |       |        |          |

|-----|-----------------------|---------------------------------------|-------|--------|----------|

| 名称  | 价格                    | 运算速度                                  | 数据处理能 | 扩展能力   | 植入系统能    |

|     | ਮ। 1 <del>ਬ</del><br> | ————————————————————————————————————— | 力     | 1) 放肥刀 | <u>力</u> |

| 单片机 | 较低                    | 慢                                     | 弱     | 一般     | 弱        |

| DSP | 较高                    | 快                                     | 很强    | 一般     | 弱        |

| ARM | 适中                    | 适中                                    | 强     | 强      | 强        |

|     |                       |                                       | ·     |        |          |

从表 2-4 中可知通常情况下这三种芯片都可以进行数据处理。单片机廉价易用,但是

运算速度较慢,受到存储空间和计算速度的影响不太适合应用于本设计; DSP 具有强大的数据处理能力和高运算速度,单纯考虑使用数据预处理功能的话,DSP 可以很好的满足这些要求,但是其外部扩展能力以及植入操作系统方面较弱,不便于二次开发; ARM的数据处理能力较强运行速度也比较快,虽然在这两个方面比不上 DSP,但是其外部扩展丰富,可以外接存储设备,特别是可以移植实时操作系统,将激光雷达后期的数据处理、数据反演、曲线绘制等逐步添加到采集系统中,提高整个激光雷达系统的性价比。结合以上几个特点,本设计选用 ARM 作为核心处理单元,构建 ARM 最小系统,根据数据量扩展外设存储设备,满足激光雷达数据采集系统的设计需要。

表 2-5 激光雷达数据采集系统具体方案 Tab. 2-5 Specific program of lidar data collection system

| 主要模块 | 使用器件 |

|------|------|

| 时序控制 | CPLD |

| 信号采集 | AD   |

| 数据缓存 | FIFO |

| 数据处理 | ARM  |

综上所述,系统总体设计具体方案如表 2-5 所示。本设计最终选定 AD 作为信号采集单元采集激光雷达回波信号;CPLD 作为时序控制单元,接收触发信号的同时向 AD 和 FIFO 提供控制信号以及时序逻辑;FIFO 为数据缓存单元,作为 AD 和 ARM 之间的接口,使得高速数据采集部分的时间和低速数据处理部分时间相对独立;ARM 作为数据处理单元,完成数据的预处理、存储、上传等功能。

## 2.3 本章小结

本章通过分析激光雷达的工作原理,激光雷达的系统整体结构以及激光雷达回波信号的特点,阐述了激光雷达数据采集系统的设计原理,提出了激光雷达数据采集系统的设计要求。根据设计要求,设计了选用 CPLD 提供系统时序逻辑,AD 作为信号采集器件,FIFO 作为数据缓存器件,ARM 作为数据处理、存储的核心处理器件的总体设计方案。根据总体设计方案,本文的第三章和第四章,分别从硬件设计和软件设计两个方面阐述该系统的组成。

## 3 激光雷达数据采集系统硬件设计

根据第二章提出的系统总体设计方案,本章主要介绍激光雷达数据采集系统的硬件构成。按照模块化思想,分别介绍了各个组成模块的功能以及硬件实现,详细阐述了各个模块的设计思路和在设计中遇到的问题以及解决方法<sup>[10,12-21]</sup>。

## 3.1 激光雷达采集系统硬件设计总体架构

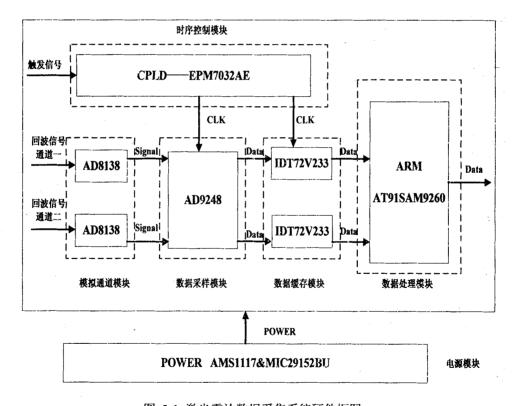

根据总体设计方案,构建了该系统的硬件总体框架。本系统主要由六大模块构成,其硬件结构框图如图 3-1 所示:包括模拟通道模块、数据采样模块、时序控制模块、数据缓存模块、数据处理模块以及电源模块。设计中主要用到的芯片包括:2 片运算放大器 AD8138 提供 AD 差分输入信号;1 片 Altera 公司 CPLD 芯片 EPM7032AE 作为时序逻辑产生器件;1 片 AD 公司的双通道模数转换器件 AD9248 作为数据采集器件;2 片 IDT 公司生产的 FIFO 芯片 IDT72V233 作为数据缓存器件;1 片 Atmel 公司 AT91SAM9260 处理器作为数据处理单元核心器件。

图 3-1 激光雷达数据采集系统硬件框图 Fig. 3-1 Hardware block diagram of lidar data acquisition system

根据总体设计,该系统的设计技术指标有以下几点:

(1) 允许输入信号幅值: ±1Vpp

- (2) 数字采样频率: 14 位 20MSPS 高速采样

- (3) 信号处理功能:数据平均

- (4) 测量精度: 2000mV/2<sup>14</sup>=2000mV/16384≈0.1mV

# 3.2 激光雷达数据采集系统各模块功能和硬件实现

## 3.2.1 模拟通道模块设计

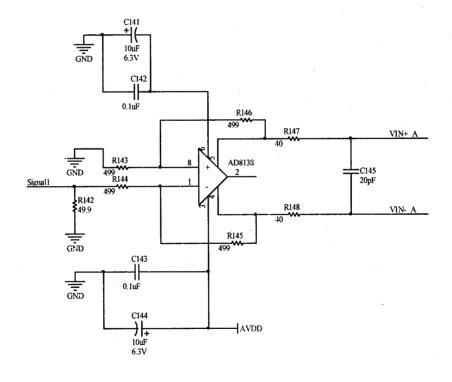

由于激光雷达回波信号表现为单端模拟信号,虽然单端方式连接较简单但抗噪性差,而且 AD9248 数据手册中强调差分输入有助于提高所采集信号的精度和准确度。该模块主要功能是将单端信号转为差分信号,为 AD9248 提供差分输入。这样可以尽量减少信号噪声以及电磁的干扰,尤其是采用差分输入方式可以将所有的偶次谐波通过正反两个输入信号基本上互相抵消。此外为了保证在高频下信号的失真最小,增强输入信号也建议在信号输入端前加上前置放大器以及 RF 变压器,将单端信号转换为差分信号再输入到 AD 芯片中。

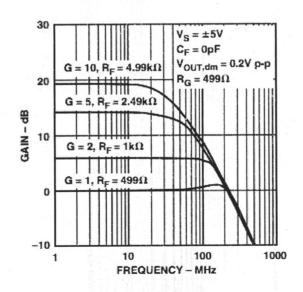

由于这个设计中的输入信号频率范围为 0-20MHz,预留方案为 50M,运放带宽应该在 100MHz 左右,为了保证运放在 100M 内有好的特性,而且由开环特性引起的误差尽可能小,选用 AD 公司的 AD8138 作为运算放大器。该放大器具有较宽的模拟带宽(320MHz,-3dB,G=1, $R_F=499\Omega$ ),其频率与增益的关系如图 3-2 所示。输入信号频率在 100M 之内几乎没有衰减,所以刚好可以满足系统设计要求。

图 3-2 频率与增益的关系 Fig. 3-2 Relation between Frequency and Gain

表 3-1 AD8138 主要特性 Tab. 3-1 Main feature of AD8138

| 14015 11141111 | •             |

|----------------|---------------|

| 性能             | 指标            |

| 带宽             | 320MHz (-3dB) |

| 输入阻抗           | $6 M\Omega$   |

| 工作温度           | -40℃~85℃      |

| 功耗             | 90mW@5V       |

| 电源供电范围         | 3V~5V         |

表 3-1 所示为 AD8138 主要特性。芯片采用 XFCB 双极工艺,容易用作单端到差分放大器的转换,简化差分信号放大和驱动。工作温度范围宽,满足激光雷达使用条件。该芯片可调整共模输出电压,外部调整增益,最大化 ADC 的性能且不需要变压器,从而保留了低频和 DC 信息。此项功能应用在激光雷达高速数据采集系统设计中,降低了单端输入情况下 AD 转换结果的二次谐波,提高了系统的信噪比(SNR)。该芯片输入阻抗高达6MΩ,可以直接与输入信号相连而省略隔离放大器,大大精简了电路结构<sup>[29]</sup>。

图 3-3 AD8138 原理图 Fig. 3-3 Schematic diagram of AD8138

整个模拟通道主要由 2 片 AD8138 组成,其电路原理图如图 3-3 所示。在此给出的是

AD9248 通道 A 的模拟通道电路原理图, B 通道的电路原理与图 3-3 类似。

1 管脚作为正向输入端接激光雷达回波信号,8 管脚作为负向输入端接地作参考。2 管脚提供一个1:1 输入方式,在本设计中空置。3 管脚作为电压正端接电源3.3V,6 管脚作为电压负端接地。4 管脚作为信号差分输出的正端,5 管脚作为差分信号输出的负端。通道传输线上的电阻为了实现阻抗匹配减少反射,电阻的大小和传输线的阻抗相等,电容主要起到滤波作用,选用高频电容,附加电感小,谐振频率高,介质损耗小,容量稳定。

## 3.2.2 数据采样模块设计

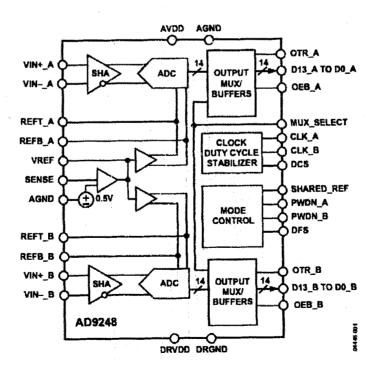

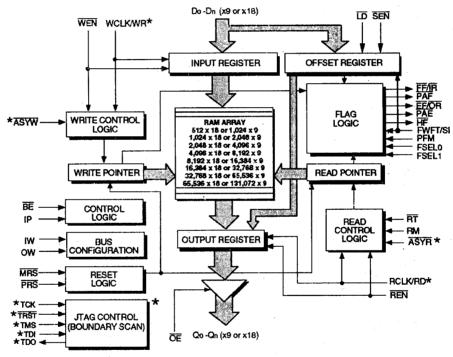

数据采样模块使用模数转换器件,根据设计要求采用 AD9248。该芯片是 ADI 公司推出的 14 位双通道数模转换芯片,芯片采用 3.3V 供电。具有 20MSPS、40MSPS 以及 65MSPS 三种采样速度,其内部结构如图 3-4 所示。它拥有两个独立的 SHA 和 ADC,一个集成在内部的参考电压。每一个通道都是一种基于流水线型的 ADC,这种流水线型结构的特点是由一系列标志 1 级、2 级等各级构成。每级的结构是相同的,包含一个采样保持电路(S/H)、一个子模数转换电路(ADC)和一个乘积数模转换器(MDAC)电路。该芯片采用多级带有输出错误纠正逻辑的差分流水线结构,从而可以提供高精度 14 位量化输出。该芯片的优点在于双通道 AD9248 可以提供与单通道 AD 转换器同样的动态性能,但是又比使用 2 个单通道 AD 芯片具有更好的抗串扰性能。可以满足激光雷达多参量探测时的使用要求。

图 3-4 AD9248 内部结构图 Fig. 3-4 Internal structure chart of AD9248

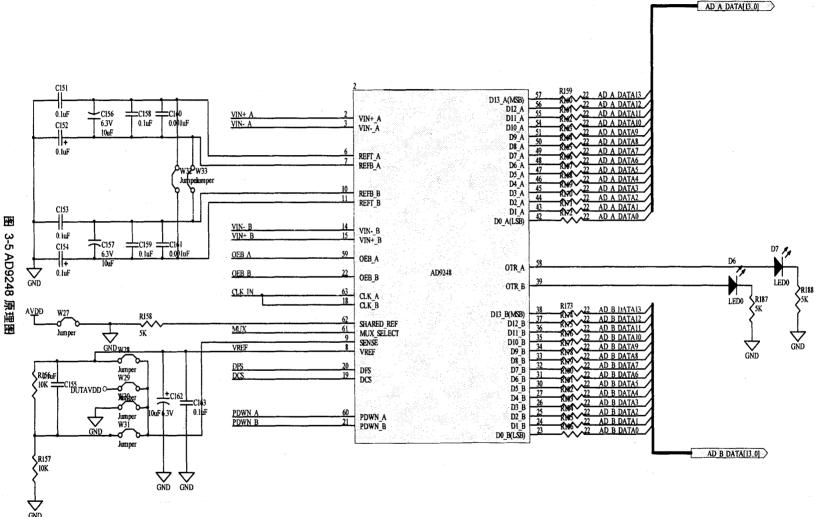

在本设计中选用 AD9248-20 作为数模转换器件。连接方式如图 3-5 所示(未包含电源和地的接法)。AD9248 的 2、3、14、15 管脚主要接收模拟输入的差分信号,此信号由 AD8138 提供,18、63 管脚连接后接满足数据采集系统采样要求的 20M 时钟信号,由 CPLD 器件 EPM7032AE 提供,此种连接方式可以保证双通道采集在时间上的同步性,也可以减少使用 CPLD 的一个控制端口。另外一些功能管脚配置也由 CPLD 器件 EPM7032AE 提供:包括 22、59 管脚数据输出使能;21、60 管脚是通道开关使能;20 管脚输出数据格式选择位;61 数据复用模式选择位。其具体的使用原则和本设计中采用的配置方式见表 3-2。

表 3-2 AD9248 主要引脚功能及配置方式 Tab. 3-2 Main pin function and collocation of AD9248

| 引脚及功能                   | 使用方法                                                     | 本设计中配<br>置方式   |

|-------------------------|----------------------------------------------------------|----------------|

| VIN+、VIN-               | 模拟差分信号输入端                                                | 接 AD8138       |

| REFT、REFB               | 外部基准电压的输入端                                               | 接地             |

| D0~D13                  | 数据输出位                                                    | 接 FIFO 的数据写入端口 |

| OEA、OEB                 | 为0时使能数据总线;                                               | 置 0            |

| 数据输出使能位                 | 为 1 时输出为高阻                                               | 且U             |

| PDWNA、PDWNB             | 为0时使能通道;                                                 | 置 0            |

| 通道关闭使能位                 | 为 1 时关闭通道。                                               | . <b>旦.</b> V  |

| DFS                     | 为0时数据输出格式为偏移二进制;                                         | 置 0            |

| 输出数据格式选择位               | 为 1 时数据输出格式为二进制补码。                                       | 且り             |

| OTR_A、OTR_B<br>溢出标志位    | 溢出时输出高电平                                                 | 接报警指示<br>灯     |

|                         | 为1时该两通道数据分别从各自通道输出;                                      |                |

| MUX_SELECT<br>数据复用模式选择位 | 为 0 时 A 通道数据从通道 B 输出, B 通道数据从通道 A 输出;该管脚接时钟时,两通道数据将复用输出数 | 置1             |

|                         | 据端口,此时输出速率是采样速率两倍                                        |                |

| SENSE                   | 为0时,使用内部参考电压                                             | 置 0            |

| 基准模式选择位                 | 为1时,使用外部参考电压                                             | 且V             |

表 3-2 中的配置方式是针对双通道同时采集时的设置方案,如果进行激光雷达实验时只需要使用其中一个通道,另一个通道不需要接入信号且操作 ARM 处理单元不读取该通道 FIFO 输出端数据即可。

Fig. 3-5 Schematic diagram of AD9248

本设计中特别要注意是参考电压的设置,AD9248 内部有一个稳定精确的 0.5V 参考电压。调整 AD9248 的参考电压可以改变信号的输入范围。本设计中参考电压的设置主要涉及 6、7、10、11 管脚分别为双通道 REFT、REFB 管脚; 62 管脚 SHARED\_REF; 9 管脚 SENSE 以及 8 管脚 VREF。参考电压由内部参考和外部参考两种,主要是改变 SENSE管脚的接法,所以本设计将这几种可能用到的方式都设计在内,用接插接的方式接通,便于使用和调试。

- (a) 当接插件 W24 接通后, SENSE 直接和 VREF 连接, 输入信号为 1Vp-p。

- (b) 当接插件 W25 接通后, SENSE 与 AVDD 接通, 属于外部电压参考, 内部电压参考 无效, 此种情况使用不多。

- (c) 当接插件 W26 接通后, SENSE 管脚接地, VREF 设置为 1V, 输入信号范围为 2Vp-p。

- (d) 当接插件 W27 接通后, SENSE 与 VREF 还有模拟地直接通过串联两个电阻接通, 其电压通过公式(3.1) 可以得到。

VREF=

$$0.5 \times (1 + \frac{R2}{R1}) = 0.5 \times (1 + \frac{10K}{10K}) = 1V$$

(3.1)

另外 AD9248 对每个通道提供了参考电压,线路原理如图 3-5 所示,电容的作用是去 耦和隔离。也可以采用效果更好的共享式电压参考方式,就是接通接插件 W28 和 W29。 两个通道的 REFT 和 REFB 分别相连,此时需要将 SHARED\_REF 管脚置高电平,接通接插件 W23,如果不使用共享式参考电压的方式,SHARED REF 管脚通常接地<sup>[30]</sup>。

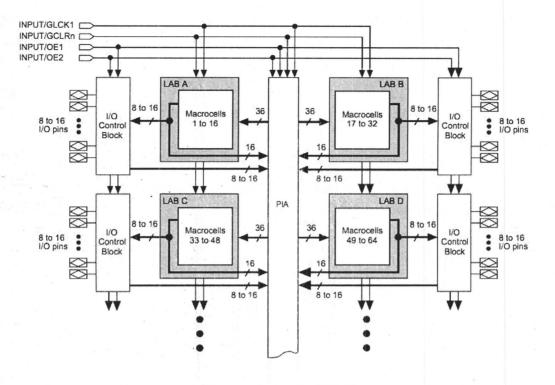

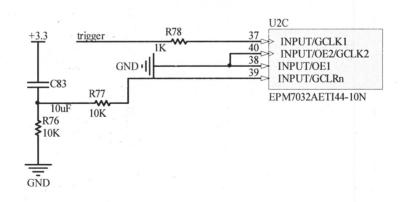

## 3.2.3 时序控制模块设计

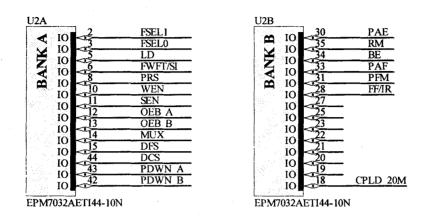

该模块主要完成两个功能:一是接收外部触发信号;一是为数据采集系统的 AD 和 FIFO 提供时序逻辑和控制信号。本设计选用 Altera 公司生产的一个 CPLD 芯片 EPM7032AE,其内部结构如图 3-6 所示。它具有以下几个方面的特点<sup>[31]</sup>:

- (1) 以第二代多阵列矩阵为基础的高性能 CMOS EPROM 器件构成,它有 600 个可用的门电路。

- (2) 引脚到引脚的逻辑延时为 5ns, 计数器工作频率为 178.6MHz。

- (3) 有可编程功率节省模式,使每个宏单元的功耗降低到50%或更低。

- (4) 可配置的扩展乘积项分配,允许向每个宏单元提供多达 32 个乘积项。

- (5) 3.3V 供电。

- (6) 有可编程保密位,全面保护专利设计。

- (7) 可通过串行或并行下载器 Byte-Blaster 下载二进制文件到 CPLD, 从而实现现场可编程。

- (8)包括4个专用输入,它们可用作通用输入或作为每个宏单元和I/O引脚的高速、全局的控制信号:包括时钟、清除和输出使能。

图 3-6 MAX7000 系列结构图 Fig. 3-6 Block diagram of MAX7000

图 3-7 所示为 CPLD 接收触发信号的原理图,37 管脚作为 CPLD 时序输入端口,用来接收外触发信号,触发信号作为 CPLD 的工作时钟,控制 CPLD 正常工作。系统采用上电复位的方式,连接 CPLD 的 39 管脚,其38 管脚和40 管脚接地。

图 3-7 CPLD 接收触发信号原理图 Fig. 3-7 Schematic diagram of receiving triggered signal

图 3-8 所示为 CPLD 产生时钟信号以及对 AD 和 FIFO 功能管脚控制的控制信号原理图。18 管脚输出 AD 以及 FIFO 写入数据所需的时钟信号,因为 AD 采样所得数据要实时

送入 FIFO, 所以两者的写时钟频率必须一样, 操作起来统一方便。其余管脚分别连接 AD 以及 FIFO 的功能选择端口, 在系统开始采集之前, 首先设定 AD 以及 FIFO 的工作模式。 另外, 在采集过程中, 控制 AD 以及 FIFO 的启停。

图 3-8 时钟信号及控制信号产生原理图

Fig. 3-8 Schematic diagram of clock signal producing and control signal producing

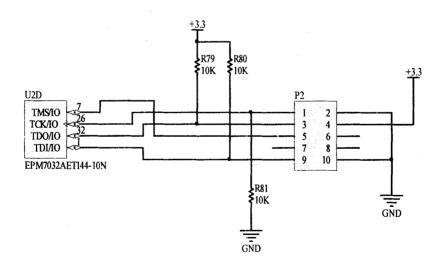

图 3-9 所示为 CPLD 程序下载原理图,通过该图的连接方式可以将开发工具中的程序 烧写到 CPLD 中。其中 1、7、26、32 管脚是程序下载部分,其对应的 10 针插头引脚定 义如表 3-3 所示。

图 3-9 CPLD 程序下载原理图

Fig. 3-9 Schematic diagram of program download of CPLD

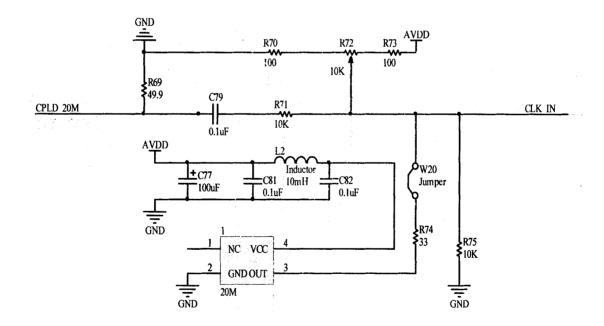

图 3-10 所示为 20M 采样频率的时序逻辑信号产生原理图。有两个部分组成:一个是通过 CPLD 产生的 20M 时钟:另一个是 20M 晶振,可以产生固定时钟,通过接插接隔开。

如果 CPLD 出现问题无法产生 20M 时钟信号或者调试需要,则接通 W17,确保系统的正常工作状态,也可以避免重复制作 PCB 板的麻烦。

表 3-3 10 针插头引脚定义

| Tab. | 3-3 | Definition | of 10 | pins |

|------|-----|------------|-------|------|

|      |     |            |       |      |

| 引脚 | 信号名 | 描述         |

|----|-----|------------|

| 1  | TCK | 时钟信号       |

| 2  | GND | 信号地        |

| 3  | TDO | 输出数据       |

| 4  | VCC | 电源         |

| 5  | TMS | JATG 状态机控制 |

| 6  | NC  | NC         |

| 7  | NC  | NC         |

| 8  | NC  | NC         |

| 9  | TDI | 输入数据       |

| 10 | GND | 信号地        |

图 3-10 固定时钟信号产生原理图 Fig. 3-10 Schematic diagram of fixed clock signal producing

在本部分设计过程中,如果单纯的实现数据采集的功能,AD 以及 FIFO 的功能管脚不需要使用 CPLD 控制,最简单的方式是需要置 0 的直接接地,需要置 1 的直接接电源,

这样可以省去大部分的 CPLD 管脚,使得硬件趋于简单,但是如此设计会给系统调试带来麻烦,也不利于后期的开发,所以采用 CPLD 控制功能管脚的方式,必要时可以通过重新烧写 CPLD 程序,实现其他方式的采集。

时序控制部分的整体原理图见附录 A-2。

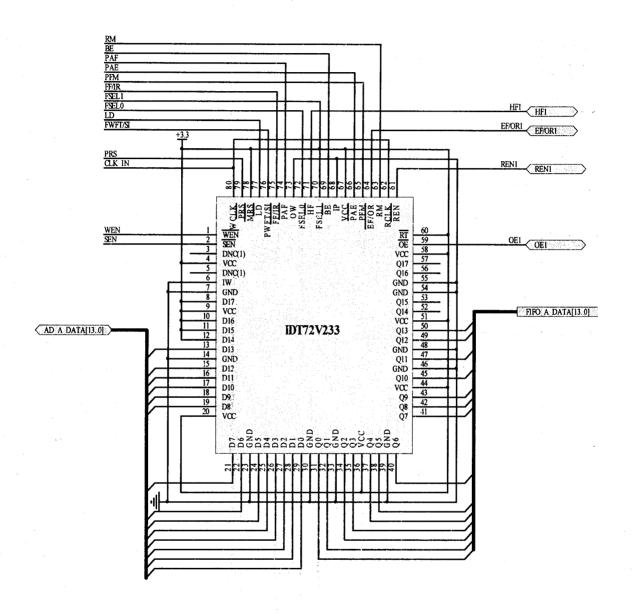

## 3.2.4 数据缓存模块设计

本模块的主要功能是作为AD器件与ARM器件的接口,起到数据缓存的作用。本设计选用的是IDT公司生产的IDT72V233,IDT72V233属于IDT公司的高密度supersyncTMII系列存储器IDT72V223~293中的一种,其存储结构为1024×18或者2048×9。其内部结构如图3-8所示。其基本功能特点如下<sup>[32]</sup>:

图 3-11 IDT72V233 的内部结构框图

Fig. 3-11 Block diagram for internal structure of IDT72V233

- (1) 对读 / 写口都可进行灵活的总线宽度设置,可选择不同的输入 / 输出数据线宽度(可在18 in 18 out; 18 in 9 out; 9 in 18 out中选择)。

- (2) 首字的写入到读出的延时很短且固定。

- (3) 操作时钟可达166MHz。

- (4) 主复位方式可提供FIFO整体清零,部分复位只清掉存储数据,但保留可编程设置项。

- (5) 几乎空/满标志置位或无效操作可选择同步或异步时间模式。

- (6) 具有两种时间工作模式,分别为IDT标准模式(采用EF和FF标志位)和FWFT 首字直传模式(采用OR和IR标志位)。

- (7) 读写操作采用独立时钟,并可异步操作。

图 3-12 FIFO 原理图 Fig. 3-12 Schematic diagram of FIFO

CPLD产生 20M 时钟信号与 AD 的 clock 端以及两个 FIFO 的 WCLK 相连,可使 FIFO 同步将 AD 采样数据写入。为了使 AD9248 两个通道 AD 同时工作,提高系统效率,设计时采用两个 FIFO 独立地将两路 AD 输出数据进行存储。由于 AD 的数据输出为 14 bit, FIFO 存储宽度为 18 bit,故在本设计中将 FIFO 输入端的空脚接地,输出端空脚悬空。连线的原理图如图 3-12 所示。该图为与 AD 通道 A 连接的 FIFO 的原理图,连接 B 通道的

FIFO 的原理图与该图类似。

表 3-4 所示为 IDT72V233 主要功能引脚的功能以及本设计中采用的配置方式:

表 3-4 FIFO 主要引脚功能及配置方式

| Tab. 3-4 Main pi | n function and | collocation of FIFO |

|------------------|----------------|---------------------|

|------------------|----------------|---------------------|

| 引脚        | 功能及使用方法    | 设计中配置方法   |  |

|-----------|------------|-----------|--|

| D0~D17    | 数据输入       | 接 AD9248  |  |

| Q0~Q17    | 数据输出       | 接 ARM     |  |

| O.D.      | 为0时使能通道    | 接 ARM 控制读 |  |

| OE        | 为1时关闭通道    | 数据        |  |

|           | 低电平时 IDT 标 |           |  |

| FWFT / SI | 准模式        | 置 0       |  |

|           | 高电平 FWFT   |           |  |

| PRS       | 部分复位 置1    |           |  |

| PFM       | 低电平异步操作    | 置 1       |  |

|           | 高电平同步操作    | 1.且       |  |

本设计针对FIFO器件的配置,主要遵循以下以个方面:

- (1)对FIFO芯片的时间运行模式、可编程标志位的时间模式、读写时钟,同步异步选择、部分复位等由CPLD控制。

- (2)由于AD9248是14bit,所以输入/输出字节宽度设定为18×18。它的存储空间可以设置为1024×18,且6号管脚(IW)和73号管脚(OW)接低电平来选择输入/输出数据的宽度为18×18。IW和OW的组合情况见表3-5。

表 3-5 数据宽度定义方式

Tab. 3-5 Definition mode of data bit

| IW | ow | 输入宽度 | 输出宽度 |

|----|----|------|------|

| L  | L  | 18   | 18   |

| Ĺ  | Н  | 18   | 9    |

| Н  | L  | 9    | 18   |

| Н  | Н  | 9    | 9    |

(3)通过65号管脚(PFM)设置同步、异步操作。同步操作时,当WEN=0时,WCLK的上升沿到来时D0~Dn的数据写入FIFO中;异步操作时,WCLK/WR的上升沿到来时D0~Dn的数据写入FIFO中。读数据时,REN=0时,RCLK的上升沿将数据读出。

- (4) 76号管脚(FWFT/SI)决定采用的模式为FWFT模式还是IDT模式。本设计中选择使用IDT模式。在此模式下,用EF来说明FIFO中为空,FF则说明FIFO中为满。

- (5)复位也有两种分为主复位和部分复位,当主复位启动后,读写指针都指向第一个数据位置,几乎空标志置低,几乎满标志和半满标志置高,同时,输入/输出的总线宽度、可编程标志位的同/异步方式以及是否需要去掉字节中的校验位均被确定,输出寄存器初始化为全零,上电即进行复位,以后才可进行写操作。而当部分复位后,只有读写指针复位,几乎空标志置低,几乎满标志和半满标志置高电平,其余各种运行方式不变,部分复位可在操作进行中进行复位,当经过编程设定的偏置值不理想时,可随时调用。系统采用上电主复位,部分控制端口由CPLD控制。

#### 3.2.5 数据处理模块设计

数据处理模块主要功能是从 FIFO 中读取缓存数据,存入相应地址单元,同序列相加后进行平均处理。

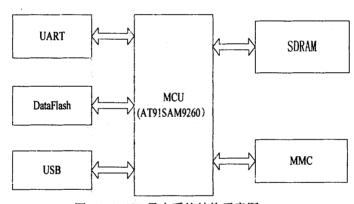

本部分设计采用 2006 年 Atmel 公司的主力推荐的工业级 ARM9 芯片 AT91SAM9260 构建最小系统,简化设计,其结构框图如图 3-13 所示。

图 3-13 ARM 最小系统结构示意图

Fig. 3-13 schematic drawing of The ARM smallest system

由图 3-13 可知处理部分最小系统包括:核心器件 AT91SAM9260;存储单元 SDRAM 和 Dataflash;通讯单元 UART、MMC 以及 USB<sup>[33-40]</sup>。

#### (1) 核心器件

该最小系统中核心器件 AT91SAM9260 是基于 ARM926EJ-S 内核的一种处理器,具备 8KB 数据缓存。该芯片主频 200MHz,包含 8KBSRAM、32 KBROM,在最高处理速度下,可实现单周期访问 SDRAM。AT91SAM9260 内部包含全功能系统控制器,从而实现对内外资源高效、系统的管理。内部包含一个复位控制器、关机控制器、时钟管理、高级中断控制器(AIC)、调试单元(DBGU)、周期间隔定时器、看门狗定时器以及实时定时器。外部总线接口丰富,方便用户进行数据采集及存储处理。其电路原理图见附录 A-3。

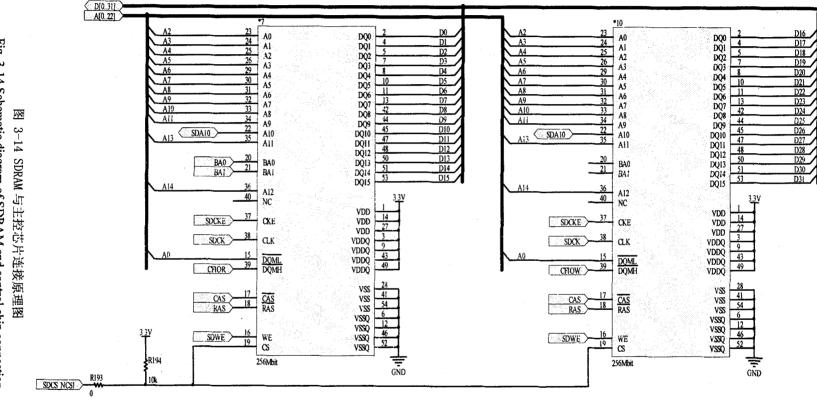

Fig. 3-14 Schematic diagram of SDRAM and control chip connection

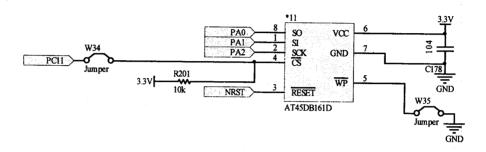

#### (2) 存储单元

在整个数据采集系统中,采样数据分辨率为 14bit。每个数据用 2Bytes 表示, 20M 采样频率时,单周期数据量为 4KBytes, AT91SAM9260 自带 8Kbytes 的存储空间能满足数据量的需要。对于数据的累加,由于单个数据累计结果采用 4Bytes 表示, 20M 采样频率时,数据量为 8KBytes,需要外部的 SDRAM,系统采用 256M×16bit 的外部 SDRAM 存储累加结果。电路原理图见图 3-14。DataFlash 用于程序的存储,采用 Atmel 公司 AT45DB161D 芯片。电路原理图见图 3-15。

图 3-15 存储单元设计原理图 Fig. 3-15 Schematic diagram of Storage unit design

图 3-16 USB 原理图 Fig. 3-16 Schematic diagram of USB

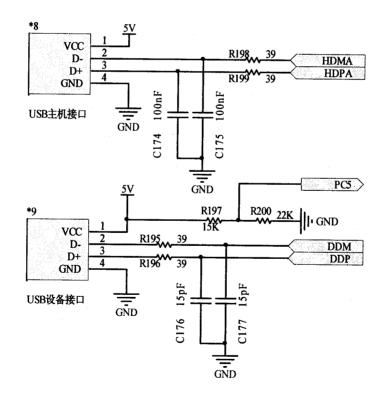

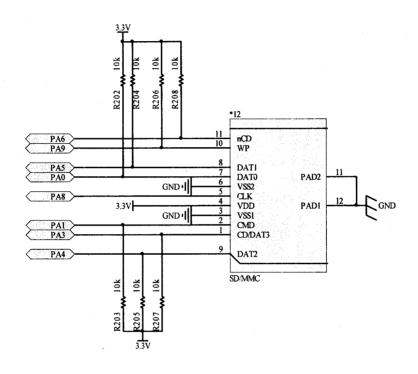

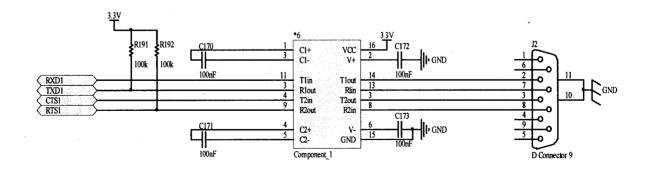

#### (3) 通讯单元

该部分设计,利用 AT91SAM9260 外设接口丰富的特点,设计了三种类型的通讯单元。包括: 232 接口; USB 主机接口和 USB 设备接口以及 MMC 存储卡。其中 USB 作为一个方便通用的传输接口,由于现如今多数的笔记本电脑都没有串行数据口,所以留有 USB 接口便于数据的存储,如图 3-16 所示; 另外 MMC 卡存储数据方便,数据方便携带,可以应用于不同条件下的激光雷达实验,如图 3-17 所示; 232 接口成熟可靠,便于 PC 机的软件开发,如图 3-18 所示。

图 3-17 MMC 原理图 Fig. 3-17 Schematic diagram of MMC

图 3-18 232 原理图 Fig. 3-18 Schematic diagram of 232

#### 3.2.6 电源模块设计

本系统的电源主要包括 5V、3.3V 以及 1.8V。USB 设备需要 5V 电压供电; AD8138、AD9248、EPM7032AE 以及 IDT72V233 工作电压均为 3.3V,AT91SAM9260 的外围器件 I/O 电压 3.3V,大部分外设芯片例如 FLASH,232,SDRAM 等芯片需要 3.3V 电源供电; AT91SAM9260 的核电压 1.8V。其电路连接如图 3-19 所示。

本设计选用 5V 开关电源,电源输入经过滤波后直接提供给需要 5V 供电的芯片使用;系统的 5V 电源经过 AS1117M3-3.3 转换成 3.3V。AS1117M3-3.3 是低功耗、低压差的线性三端稳压器。其电源的功耗可以由内部限定,输出的电流值可以达到 800mA,同时芯片的内部设计使得其具有很强的热保护和限制电流的功能。表 3-6 所示为 AS1117M3-3.3 的主要指标。

表 3-6 AS1117M 主要指标 Tab. 3-6 Main feature of AS1117M

| 性能      | 指标          |  |  |

|---------|-------------|--|--|

| 输出电压精度  | 1%          |  |  |

| 工作温度    | -65°C~150°C |  |  |

| ESD 额定值 | >2kV        |  |  |

| 输入最大电压  | 20V         |  |  |

系统的 5V 电源经过 MIC2915BU 芯片获得 ARM 工作的核电压 1.8V。MIC29152BU 芯片是高电流、高精度、低压差稳压器。其、高电流能力达到 1.5A,输出电压的精度在 ±1%以内,输出电流可达 800mA。其各管脚定义如表 3-7 所示。本设计中采用电感是为了降低电源系统扰动和噪声的影响。

表 3-7 MIC29152BU 管脚定义 Tab. 3-7 the definition of pins of MIC29152BU

| 管脚号 | 功能    |  |

|-----|-------|--|

| 1   | 启动    |  |

| 2   | 电源输入端 |  |

| 3   | 接地    |  |

| 4   | 电压输出端 |  |

| 5   | 标志位   |  |

图 3-19 电源模块原理图 Fig. 3-19 Schematic diagram of power module

## 3.3 激光雷达数据采集系统硬件抗干扰性设计

本设计的实现过程中,另一个重点是 PCB 的绘制。由于本设计为 20M 采样频率,而且涉及到高速、高精度的数据传输,所以要想保证信号的完整性,至少要绘制 4 层电路板。将电路板的信号分为上下两层,中间一层电源层,一层地层。布局遵循总的原则是:连线尽可能短,关键信号线最短;交叉线少,过孔最少;底层和电源层之间不能有连线;模拟信号与数字信号分开;增加线宽,降低其特性阻抗;重要信号间,可采用平行地线的方法隔离;尽可能少折线,不走直角走线,少走过孔。要特别注意以下几个方面的问题: [25, 41-47]

#### (1) 电源和地线的处理

为了降低并抑制整个系统的噪声,其系统电源和地的处理尤为重要。采用的方法是在电源、地线之间加去耦电容。设计时应在每个电源引脚都就近接上去耦电容,并尽量加宽电源、地线宽度,最好是地线比电源线宽。数字电路部分可用大面积铜层做地线,并在板上把没有用上的地方都与地相连接,以作为地线使用。

## (2) 模拟电路和数字电路的共地处理

本系统是由数字电路和模拟电路混合构成的,因此,在 PCB 设计时要考虑他们之间的互相干扰问题。对信号线来说,高频信号线要尽可能远离敏感的模拟电路器件,而且走线要尽可能短而等长。对地线来说,板内数字地和模拟地是分开的,应采用单点接地的方式,并通过一个磁珠将两者连接起来。事实上,整个 PCB 对外界应只有一个结点。

#### (3) 过孔的处理

高速数字电路中,过孔的寄生电感往往会给电路带来较大的负面影响。因此,在 PCB 设计中尽量做到: PCB 板上的信号走线尽量不换层,也就是说,尽量不要使用不必要的过孔。电源和地要就近打过孔,过孔和管脚之间的引线越短越好,因为它们会导致电感的增加。在信号换层的过孔附近放置一些接地的过孔,以便为信号提供最近的回路。

## 3.4 本章小结

本章主要介绍了激光雷达高速数据采集系统的硬件组成,分模块介绍了数据采集系统的设计思路,分别给出了每个模块的电路原理图,并且根据原理图全面阐述了设计中遇到的问题和解决的办法以及连接方式和芯片之间的逻辑控制关系,另外针对 PCB 布局方面要注意的事项给出了参考意见。

# 4 激光雷达数据采集系统软件设计

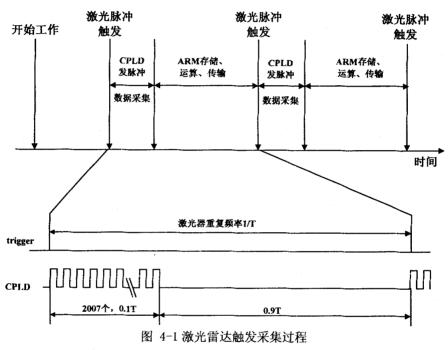

激光雷达数据采集系统的软件设计主要包括两部分的内容:一部分是 CPLD 程序设计,该部分主要功能是接收外部触发信号,产生系统时序逻辑;另一部分是 ARM 程序设计,该部分主要功能是读取 FIFO 中暂存的数据进行数据预处理。本章在硬件设计的基础上,编写了该系统主要部分的软件程序。详尽的介绍了各个主要部分的程序编写流程,以及程序编写过程中需要注意的问题。

Fig. 4-1 The processing of lidar data trigger acquisition

图 4-1 所示为激光雷达触发采集过程,整个软件程序的编写要遵循这个过程。在激光雷达数据采集过程中,激光器每次发射一个激光脉冲,便有一个外部触发信号送到了数据采集系统,CPLD 接收外部触发信号同时控制信号采集系统的开启,CPLD 产生满足采样要求的 clock 提供给 AD 以及 FIFO。采样信号经过 AD 转换后直接送入 FIFO 进行暂存,后期 ARM 从 FIFO 将数据读出并进行数据处理和传送。

以西安理工大学激光雷达遥测研究中心采集米散射激光雷达回波信号为例,其激光脉冲重复频率为 1kHz,用其探测气溶胶时产生 1 路回波信号和 1 路触发信号。系统上电后设置采集间隔为 5 分钟,则 CPLD 在接收到触发脉冲后,连续向 AD 的 clock 发送周期为50ns 的脉冲2007个(AD 的转换周期为7个时钟信号),按照20M 的采样频率需要100us,在余下的900us 即下一个触发脉冲来临之前ARM完成存储和运算。当连续采集10s后,共采集到10000组数据,满足数据处理需要的数据量,利用剩下的290s将数据上传到PC

机。

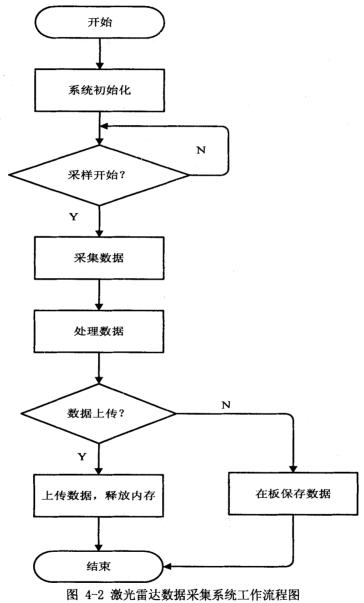

如图 4-2 所示为激光雷达数据采集系统的工作流程。系统上电后,首先进行系统初始 化,等待外部触发信号控制系统启停,当接收到外部触发信号的同时开始进行数据采集, 而后进行数据处理,最后等待上位机指令,是将数据存在系统自带存储单元还是送到 PC 机,一次工作结束。

Fig. 4-2 Workflow diagram for data collection system of lidar

数据采集和数据处理是整个系统程序的核心部分。数据采集主要由 CPLD 产生 AD和 FIFO 所需要的时序逻辑以及其功能管脚设置,控制其采集启停、存储等功能;数据处

理部分主要是 ARM 从 FIFO 中读取数据,按照时间先后顺序存入相应的地址单元,进行平均处理运算。下面将详细介绍这两个部分的程序编写流程以及程序编写中需要注意的问题。

# 4.1 激光雷达采集系统数据采集程序设计

数据采集程序主要包括 AD 采样和 FIFO 存储需要的时序逻辑以及提供 AD 和 FIFO 功能管脚的逻辑控制。CPLD 有别于 ARM 和单片机,其编程语言为 verilog 硬件描述语言,编写时采用软件编写,但程序烧写入 CPLD 芯片之后,CPLD 作为一个硬件使用。由于 CPLD 对于 AD 以及 FIFO 在功能设置上有一定区别,本节将设计分开说明。

#### 4.1.1 AD 采集程序设计

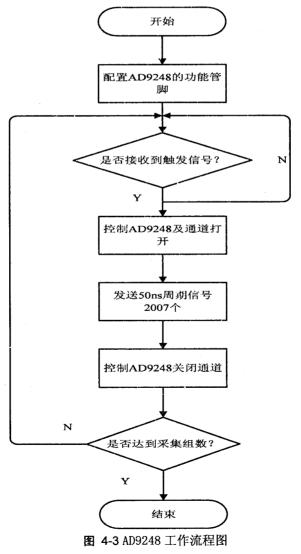

CPLD对 AD 芯片的控制流程图如图 4-3 所示。

Fig. 4-3 The flow chart of AD9248

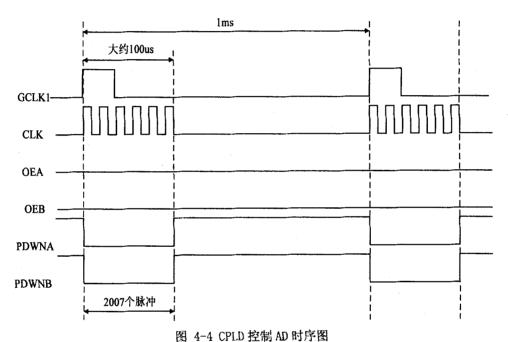

系统开始工作,CPLD 按照表 3-2 所示的配置方式配置 AD9248 的功能管脚,主要包括数据转换方式设置以及数据复用模式选择。图 4-4 所示为 CPLD 控制 AD 的时序图。当 CPLD 的 GCLK1 接收到外部触发信号的同时, CPLD 的 42、43 管脚控制 AD9248 的PDWN 端口变为低电平开启 AD 通道,于此同时 CPLD 的 18 管脚向 AD9248 的 clock 端口发送周期为 50ns 占空比为 50%的时钟信号 2007 个。根据 AD9248 的时序图(如图 4-5 所示),采样需要 7 个时钟周期,350ns 时间后输出端接收到有效信号的数据,数据处理时候剔除前 7 个无效数据。等待 2007 个数据发送完毕,CPLD 的 42、43 管脚控制 AD9248 的 PDWN 端口变为高电平,控制 AD9248 关闭通道,单组数据采集完毕。当达到采集数据的组数后,AD 采样结束。

Fig. 4-4 Timing sequence chart of AD controled by CPLD

图 4-5 AD9248 时序图 Fig. 4-5 Timing sequence chart of AD9248

#### 4.1.2 FIF0 缓存程序设计

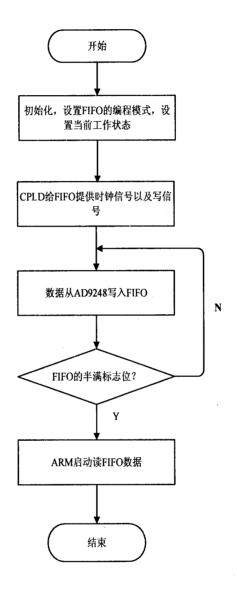

图 4-6 所示为 CPLD 控制 FIFO 的控制流程图。

图 4-6 FIFO 工作流程图 Fig. 4-6 The flow chart of FIFO

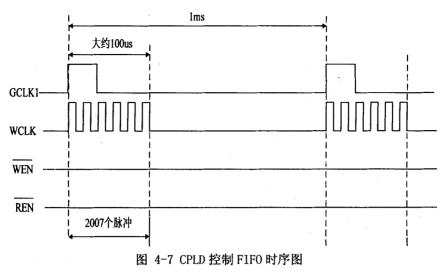

系统开始后,CPLD 参照表 3-4 所示的配置方式配置了 FIFO 的功能管脚。主要包括 FIFO 的异步传输、工作模式等。图 4-7 所示为 CPLD 控制 FIFO 的时序图。在 CPLD 给 AD 提供时钟信号的同时,将时钟信号也提供给 FIFO 器件的 WCLK 端口,数据从 AD9248 写入 FIFO。CPLD 控制WEN和REN为低电平。ARM 判断 FIFO 的半满标志位信息发送 RCLK 所需的低速时钟信号从 FIFO 中读取数据。

Fig. 4-7 Timing sequence chart of FIFO controled by CPLD

# 4.2 激光雷达采集系统数据处理程序设计

数据处理部分主要在 AT91SAM9260 构建的最小系统内完成。对于本系统而言,不需要使用操作系统,可采用简单的单线程设计编程。其主要是等待 FIFO 状态指示位的信号,将 FIFO 中的数据读出,进行相应的平均处理。通常情况激光雷达实验获得数据的过程中采用的平均处理算法包括累加平均,加权平均和算术平均。主要目的是消除激光雷达数据采集中存在系统误差、随机误差等,因为单次回波信号不能准确的反演大气特征参数,需要采集多组数据进行平均处理后使用。为了更好的说明哪种方法更适合激光雷达采集系统的预处理要求,利用现有设备采集了散射激光雷达 2010 年 11 月 28 日晚 21 点 27 分的原始的 10000 组数据(备注:当日晴天,温度 2℃~15℃)分别运用三种平均方法进行了分析[49]。

# 4.2.1 数据预处理方法分析

#### (1) 累加平均

由于激光雷达的特殊性,实时数据量大,而且具有大容量存储功能和高计算速度的核心处理单元还未广泛使用的时候,定义了一种特殊的数据处理方式,称之为累加平均。其公式如(4.1)所示。

$$\overline{D} = \frac{1}{2} \left\{ \frac{1}{2} \left[ \frac{1}{2} (D_1 + D_2) + D_3 \right] + \dots + D_n \right\}$$

(4.1)

其展开式如公式(4.2)所示。从展开式中可以发现该种处理方式存在一个问题:最后一组数据的权重占整个数据的二分之一,最后一组或几组数据在采集过程中如果出现了大的

误差或者错误将直接影响到最终的测量结果。

$$\overline{D} = \frac{1}{2}D_n + \frac{1}{2^2}D_{n-1} + \dots + \frac{1}{2^{n-2}}D_3 + \frac{1}{2^{n-1}}(D_1 + D_2)$$

(4.2)

由于大气变化缓慢,可以认为激光雷达数据在一定时间内基本保持稳定,另外具有大存储量和高计算速度的核心处理单元芯片没有问世或者成本较高的时候,多采用这种方法进行采集卡的数据预处理。但是这种方法还是存在一定的局限性,使用这种方法不利于系统误差和随机误差的消除,甚至产生错误。

图 4-8 累加平均波形图 Fig. 4-8 Waveform graph of progressive average

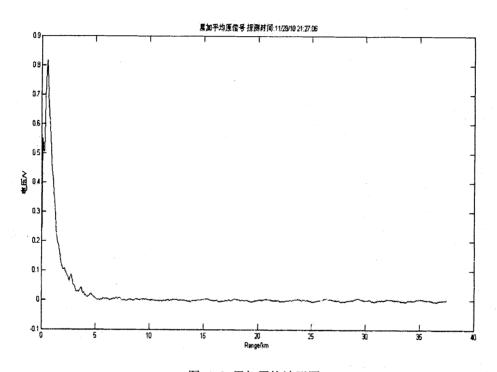

图 4-8 所示为米散射激光雷达 10000 组数据累加平均效果图, 纵坐标为电压幅值, 横坐标为测量点数 (时间)。由图可知其数据波形与图 2-2 所示的示波器采集到的波形形状上一致, 表现为高斯脉冲。但是低电平位置存在突起和毛刺, 部分误差可能没有消除。由于不能清楚的表现这种方法的优劣, 通常情况是将数据变换到频域情况下分析, 但是激光雷达有其特殊性, 通过数据反演可以看出数据的好坏。图 4-9 为利用累加平均数据反演的激光雷达距离平方校正信号(后文简称 SCSR), 横坐标表示探测距离, 纵坐标表示 SCSR。由图可知经过累加平均后的数据, 反演的有效探测距离为 5km 左右, 但这 5km 的反演效果非常不理想。在常规激光雷达实验过程中, 获得类似的实验结果, 基本可以判定为效果差或者数据无效。

图 4-9 累加平均数据反演图 Fig. 4-9 Data retrieval chart of cumulative average

本算法的好处在于十分简单便于在硬件上实现,对于存储空间的要求较低,且能够容易实时显示出每次处理的结果。但是本算法中后期数据的权重会过大,对于后期采集的数据依赖性较大,如果后期的采集过程中出现问题那将对预处理的结果产生严重的影响。

#### (2) 加权平均

针对累加平均存在的权重问题,一种新的平均算法被提出,即能保证权重合理分配又能进行方便的平均运算,其计算公式如(4.3)所示。此方法考虑到了后期采集数据的权重问题,较累加平均方法更适用于回波数据的处理,但是由于每组数据的权重会根据数据组数的增加而发生改变,所以不能进行一边读取数据一边处理数据的操作。

$$\overline{D} = \frac{1}{\sum_{n=1}^{n} n} D_1 + \frac{2}{\sum_{n=1}^{n} n} D_2 + \dots + \frac{n}{\sum_{n=1}^{n} n} D_n$$

(4.3)

本算法是在累加平均的基础上做了一个修改,改变了每组数据的权重,使得后期采集到的数据的权重降低而前期采集到的数据的权重有所增加。本算法中第n组数据的权重为n/∑n。本算法不仅考虑到了激光雷达后期数据较前期数据更具有可靠性而且后期数据的权重不会过大,能够有较好的平滑效果。

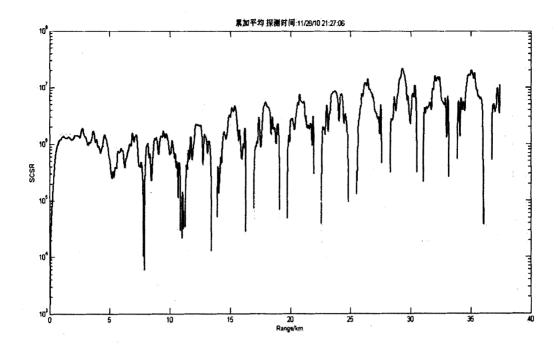

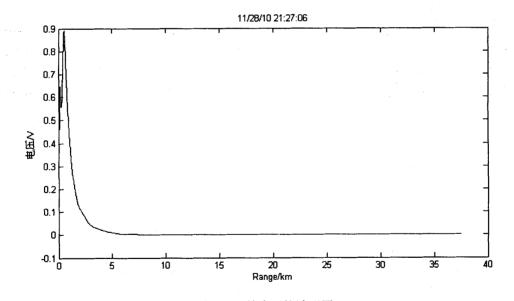

图 4-10 所示为米散射激光雷达 10000 组数据加权平均效果图,由图可知其数据波形与图 2-2 所示的示波器采集到的波形形状上一致,噪声干扰得到了有效的滤除,特征波形明显,表现为高斯脉冲。与图 4-8 相比低电平位置几乎不存在突起和毛刺,表现为一条直

#### 线,误差消除效果好。

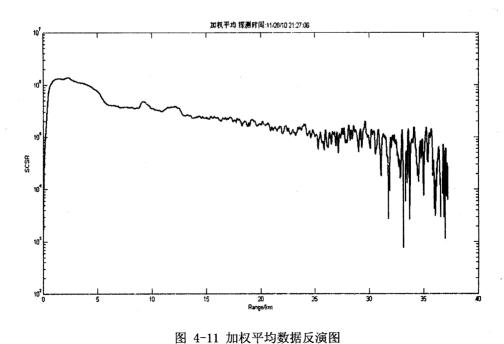

图 4-11 为加权平均数据反演 SCSR,可知经过加权平均后的数据,反演的有效探测 距离可以达到 25km 左右。观测当日为晴天,理论探测高度应该可以达到这个位置,证明 累加平均的算法在预处理过程中不太适用。

Fig. 4-10 Waveform graph of weighted average

Fig. 4-11 Data retrieval chart of weighted average

该方法的好处在于平衡了由于累加平均权重不同所产生的问题,但是硬件上不容易实现,计算量较大,对硬件的存储量和计算能力要求较高

#### (3) 算术平均

算术平均是最简单也最常用的一种平均方式,其公式如(4.4)所示。其核心思想是 将噪声看成是服从期望为零的正态分布的高斯噪声,所以将足够大组数据进行算数平均之 后从理论上可以消除高斯噪声。

$$\bar{D} = \frac{\sum_{n=1}^{n} D_n}{n} \tag{4.4}$$

本方法容易在硬件上实现,加权平均算法的权重改变的问题也可以避免。每组数据具有相同的权重,对后期采集数据的依赖性小,虽然可能由于后期权重过小,不能及时反映出大气情况的变化,并且激光雷达在后期工作较前期更加稳定应加重后期采集数据的权重。但是由于数据采集的速度很快,在一次数据采集的过程中可以近似的认为大气的环境并没有发生变化。另外由于激光雷达是精密仪器,在开始采集之后很快就会进入稳定期,只要不受到外界的突然干扰,其前后期采集的数据的稳定性应该是相当的。

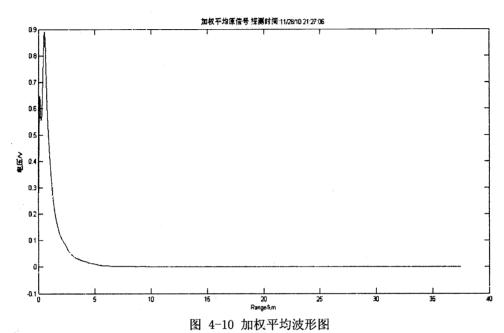

图 4-12 算术平均波形图 Fig. 4-12 Waveform graph of arithmetic average

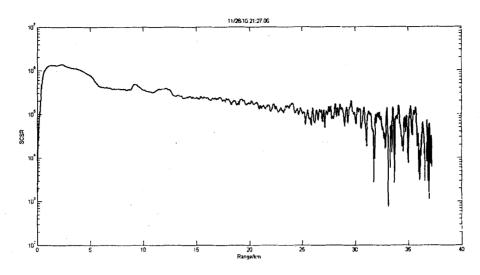

图 4-12 所示为米散射激光雷达 10000 组数据算术平均效果图,由图可知其数据波形与图 2-2 所示的示波器采集到的波形形状上一致,表现为高斯脉冲。效果与图 4-10 相同,低电平位置几乎不存在突起和毛刺,表现为一条直线,误差消除效果好。图 4-13 为算术平均数据反演 SCSR,可以看出经过算术平均后的数据,反演的有效探测距离可以达到 25km 左右。从图 4-11 以及图 4-13 中可以看到,在 10km 到 15km 范围内应该存在气溶

胶聚集区域,可能是卷云。

图 4-13 算术平均数据反演图

Fig. 4-13 Data retrieval chart of arithmetic average

综合以上讨论的三种情况,表 4-1 总结了三种算法的特点及针对激光雷达的使用效果。由表 4-1 可知,累加平均的效果较差,放弃使用。加权平均和算术平均的方法从反演的效果图中可以看出效果一致,都可以作为在板顶处理算法的方法。但是相对算术平均而言加权平均需要硬件的内存空间较大,而且操作起来比算术平均复杂,所以通过分析最终提出算术平均的方法作为激光雷达数据采集系统的在板顶处理方法。

表 4-1 三种平均方式对比表 Tab. 4-1 Table for comparison of three average mode

|         | 加权平均 | 算术平均 | 累加平均 |

|---------|------|------|------|

| 计算速度    | 慢    | 中    | 快    |

| 需要存储空间  | 大    | 中    | 小    |

| 滤除噪声有效性 | 较好   | 较好   | 一般   |

| 实现难易性   | 较难   | 简单   | 简单   |

## 4.2.2 程序设计

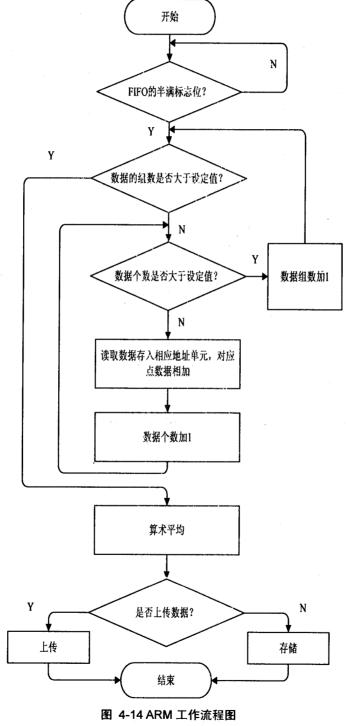

算术平均方法主要在 AT91SAM9260 中完成。ARM 接收到 FIFO 半满标志位的信号, 开始从 FIFO 中读取数据先存储在 AT91SAM9260 自带的 SRAM 内,单周期数据采集完成 后,进行算数平均运算,得到一组数据,存入相应的地址单元,根据需求判断是放在外部 SRAM 中,还是上传到 PC 机。其流程图如图 4-12 所示。 本程序对一边读取一边处理数据方案的实现是通过三个循环的嵌套实现的。最外层的循环是一个死循环,保证硬件程序一直在执行中。第二层循环是一个以读取组数为循环变量的 for 循环。最内层循环是以读取数据在本组的第几个为循环变量的 for 循环。而读取数据子函数和对数据进行处理的过程都是在最内层循环中进行的。

Fig. 4-14 The flow chart of FIFO

## 4.3 本章小结

本章主要介绍了激光雷达高速数据采集系统的软件部分设计,通过上述对各模块部分程序的设计,基本可以实现高速采样的功能,并达到设计的要求。给出了各个主要部分的流程图,并进行了详细的说明,同时在Quartus II 平台下结合Verilog语言,编写了该系统的时序逻辑产生程序。

# 5 激光雷达数据采集系统的改进与优化

## 5.1 方案改进与优化

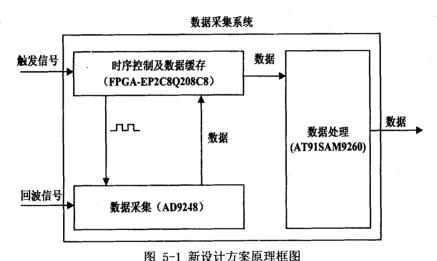

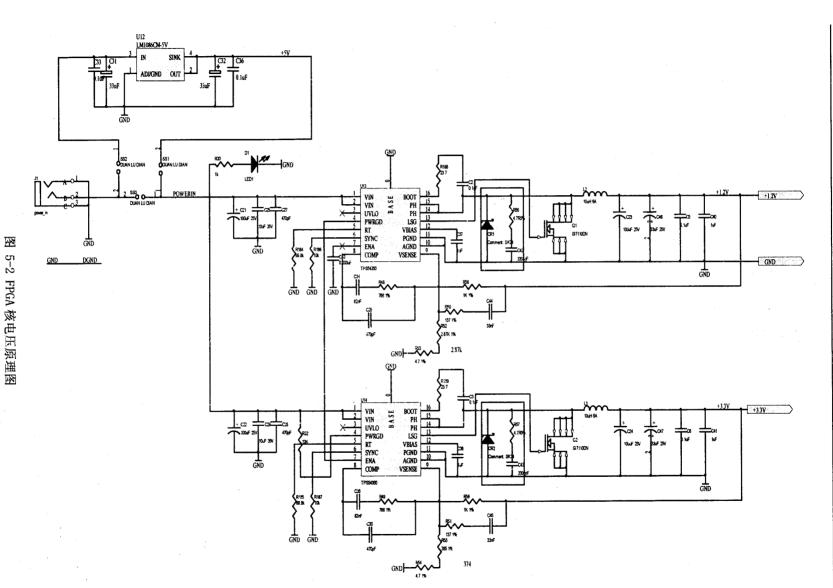

在原设计中采用的 CPLD 器件功能相对 FPGA 功能较弱,不具备植入内核的能力,而且 FIFO 芯片价格昂贵。针对这个问题,本章给出了一种改进方案,总体结构仍旧采用现有的设计思路,系统仍旧采用在板存储器的方式,方案如图 5-1 所示。AD 仍然沿用 AD9248;CPLD 器件换成 FPGA 器件 EP2C8Q208C8。EP2C8Q208C8 是 Altera 公司的 CycloneII 系列产品,逻辑容量较大。由 LAB、IOB、块状 RAM、乘法器模块、PLL 等基本的可编程模块组成。其主要技术参数为:系统逻辑单元 8256 个,RAM 容量 4Kbytes,block36 个,嵌入式乘法器 18 个,PLL2 个,最大用户 I/0 口为 182。利用该 FPGA 来代替 CPLD 产生AD 采样时钟并且在 FPGA 中嵌入内核构建一个 FIFO 来取代硬件 FIFO,这样在电路板设计上减少了两个 FIFO 器件,降低了布线的要求,但是此方法增加了软件编程的难度。

Fig. 5-1 New design principle diagram

系统接收外部触发信号控制采集系统开启,FPGA 提供 AD 采集的时序逻辑,AD 采集到的数据送入 FPGA 设置的 FIFO 器件中。在该方案中需要在 FPGA 内植入一个内核,设计一个 FIFO 存储器,另外该 FPGA 核电压为 1.2V,外围器件为 3.3V,所以需要利用新的电源产生方式,产生 1.2V 电压。

## 5.2 改进方案的实现

## 5.2.1 FIF0 存储器设计

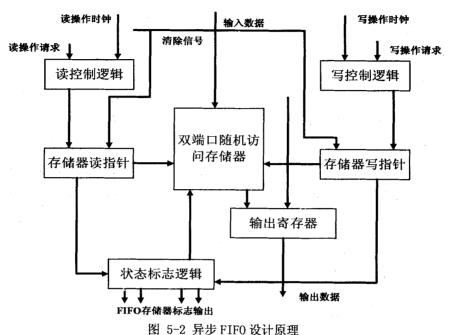

本系统采用的是异步 FIFO 器件,采用自动寻址方式实现先入先出功能。本设计原理如图 5-2 所示。利用双端口随机访问存储器模块,在数据输入端添加读操作的控制逻辑与

地址指针控制器和写操作逻辑与地址指针控制器,两端共用复位信号。在数据输出端,添加一个输出寄存器保证输出数据的稳定性,利用状态标志逻辑输出 FIFO 存储器的状态信息。

Fig. 5-2 The principle of Asynchronous FIFO design

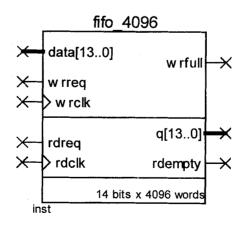

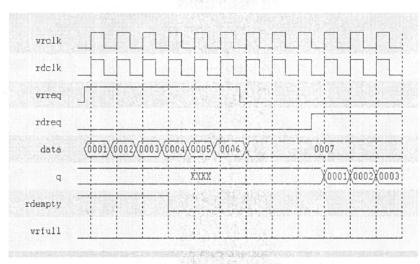

对植入的 FIFO 存储芯片,利用 QutuersII 平台仿真了其时序图,图 5-3 所示为 FIFO 的电路符号。其中 data[13..0]为数据写入端,q[13..0]为数据读出端,wrfull 为存储器满信号输出端,rdempty 为存储器空信号输出端,wrreq 为写信号输入端,rdreq 为读信号输入端,wrclk 为写信号时钟信号输入端,rdclk 为读信号时钟信号输入端。

图 5-3 FIFO 电路符号 Fig. 5-3 The circuit symbol of FIFO

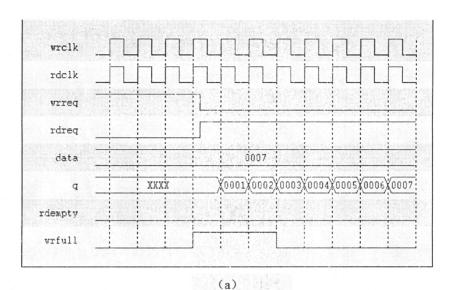

图 5-4 所示为 FIFO 的时序仿真图。由(a)可知当 wrreq 为 0 且 rdreq 为 1 时,读端口 q 读出数据; 当 wrfull 为 1 时,存储器空间为满。由(b)可知当 wrreq 为 1 且 rdreq 为 0 时,写端口 data 将数据写入; 当 rdempty 为 1 时,存储空间为空

(b) 图 5-4 FIFO 仿真时序图 Fig. 5-4 Timing sequence chart of FIFO

# 5.2.2 电源设计

图 5-4 为新的核电压产生原理图。采用 TI 公司生产的芯片 TPS54350, 其输出电流是 3A, 输入电压是 4.5-20V, 输出电压可以达到 0.89V, 正好符合设计要求, 所以 FPGA 以及 ARM 的核电压都可以由 5V 电源经过 TPS54350 得到。图中给出的是产生 FPGA 需要的 1.2V 核电压以及外围器件 3.3V 电压的核心电压模块, ARM 的核电压同理可以得到。

Fig. 5-2 Schematic diagram of FPGA power

# 5.3 本章小结

本章根据原设计中存在的问题,设计了一种改进方案。设计了利用 FPGA 代替 CPLD 以及 FIFO 的方法,核电压产生部分的原理图,并做了详细的说明,设计了 FIFO 软核,仿真了 FIFO 的时序,满足设计要求。

# 6 总结与展望

## 6.1 总结

本文主要完成了激光雷达高速数据采集系统的整体设计,包括系统的硬件结构设计以及系统的软件程序设计。在阐述激光雷达原理以及回波信号的特点的基础上,分模块介绍了数据采集系统的设计思路,分别给出了每个模块的电路原理,并且根据原理图全面阐述了设计中遇到的问题和解决的办法,详细说明了芯片连接方式以及逻辑控制关系,另外针对PCB布局方面要注意的事项给出了参考意见。在Quartus II 平台下结合Verilog语言,编写了该系统的时序逻辑产生程序。根据原设计中存在的不足,设计了利用FPGA取代CPLD和FIFO的系统改进方法,即保持原有CPLD提供时序逻辑和控制的功能,同时给FPGA植入软核搭建一个异步FIFO。

本文基于ARM技术并结合CPLD作为系统逻辑控制,设计双通道采样频率为20MSPS,外触发启动采集的方式,全部逻辑控制采用硬件完成,而且具备在板算术平均功能。前端的AD采集部分和后端的ARM数据处理部分是两个单独的个体,可以分开进行二次开发。可以更换ARM最小系统为DSP最小系统,应用于其他场合的数据采集。对于不同类型的激光雷达具有通用性和参考价值,对前期特征设置稍做修改就可以使用于其他的激光雷达系统。

#### 6.2 展望

在课题的研究过程中,由于时间与实验条件的限制,需要在以下几个方面做更深入的研究和完善:

- (1) 调试数据采集系统的各项性能指标,进行激光雷达实验。

- (2) 完善系统功能,利用 ARM 外设丰富的特点移植实时操作系统,增加多功能端口,实时显示激光雷达信号特征和反演结果。

- (3) 进一步完善数据预处理的算法。

# 致谢

在这个春暖花开的季节,我完成了硕士论文。在此首先感谢我的导师华灯鑫教授。本论文是在华灯鑫教授的细心指导下和耐心教诲下完成的。在攻读硕士的两年多期间,华老师严谨的治学态度,优良的学术作风,一丝不苟的敬业精神时刻鞭策着我努力前行。在生活和学习方面给予我莫大的关怀。俗话说:"一日为师,终身为父。"我将时刻铭记华老师的教诲,在今后的学习生活中秉承这种优良的作风和求实创新的敬业精神。

在本论文研究过程中,李大成老师、辛文辉老师、周志荣博士对于本论文的完成给予了悉心的指导和帮助,在此致以深深的谢意。另外,毛建东博士、王玉峰博士、宋跃辉博士、李仕春博士、陈浩博士、谭林秋博士、王鹏、王鸣、田甲星、王萌、巩鑫、刘才轩、田小雨、唐杰、强力虎、张守强在论文的完成过程中提出宝贵的意见,帮助论文的完善和提高,在此一并表示谢意。

衷心感谢我的父母、亲人以及女朋友多年来对我的关怀,在我求学的道路上给我太多的支持,每次看到他们期望的目光,就更加坚定了自己的想法和信念,使我可以义无反顾的面对人生道路上的种种困难。

衷心感谢西安理工大学以及各位老师在我多年来的学习中给予的教诲和帮助,感谢陪伴我多年的同窗好友,是我们的互相帮助,大家共同走过了每一个艰难的时刻。

最后,再一次衷心感谢所有关心我、支持我的老师同学和我的朋友们,感谢审阅本文的各位专家、老师付出的辛勤劳动。

# 参考文献

- 【1】 阎吉祥等,环境监测激光雷达[M],北京市:科学出版社,2001.

- 【2】 丁红星. 激光雷达对苏州城区对流层气溶胶的观测[D]. 苏州大学, 2004.

- 【3】 曹立宁. 激光雷达数据采集系统与数据处理系统的研究[D]. 西安理工大学, 2010.

- 【4】 张天佑. 激光雷达数据的高精度高速采集及可视化的研究[D]. 西安理工大学, 2009.

- **KOBAYASHI.** DHAT. Ultraviolet Rayleigh Mie lidar by use of a multicavity Fabry Perot filter for accurate temperature profiling of the troposphere[J]. 2005,30(44):6474-6478.

- [6] MASAHARU IYTT. Ultraviolet High-Spectral-Resolution Lidar with Fabry-Perot Filter for Accurate Measurement of Extinction and Lidar Ratio[J]. Japanese Journal of Applied Physics, 2005,5A(44):3063-3067.

- [7] ARIEL COHEN JACA. Atmospheric temperature profiles from lidar measurements of rotational Raman and elastic scattering[J].

- 【8】 王鸣. 微脉冲Mie散射激光雷达系统集成技术的研究[D]. 西安理工大学, 2011.

- 【9】 张云鹏,周军,黄春明. 激光雷达的高速数据采集系统设计[J]. 计算机测量与控制, 2006(2):265-267.

- 【10】 张玉静. 激光雷达信号的高速高精度数据采集系统[D]. 西安电子科技大学, 2009.

- [11] LICEL. Licel Euro Price List[EB/OL]. http://www.licel.com/.

- 【12】 刘思久, 汪秀丰, 左长魁, 等. 支持USB接口50MHz高速数据采集器[J]. 电子测量技术, 2004(2):61-62.

- 【13】 姚利民, 孙逢春, 李军求, 等. 用双端口RAM实现与PCI总线接口的数据通讯[J]. 电子技术应用, 2006(8):5-7.

- 【14】 陈光成. 用FIFO实现A/D与ARM处理器的接口[J]. 单片机与嵌入式系统应用, 2006(11):69-70.

- 【15】 闻路红, 童卫旗, 陈桂林. 用FIFO设计A/D与DSP之间的接口[J]. 国外电子元器件, 2004(2):26-28.

- 【16】 张洪润, 张亚凡主. FPGA\CPLD应用设计200例: 上册[M]. 北京市: 北京航空航天大学出版社, 2009.

- 【17】 张洪润, 张亚凡主. FPGA/CPLD应用设计200例: 下册[M]. 北京市: 北京航空航天大学出版社, 2009.

- 【18】 李佳. ARM系列处理器应用技术完全手册[M]. 北京市: 人民邮电出版社, 2006.

- 【19】 张绮文. ARM嵌入式应用开发完全自学手册[M]. 北京市: 电子工业出版社, 2009.

- 【20】 吕志鹏. 16位微处理器在FPGA上的设计与原理实现[D]. 清华大学, 2004.

- 【21】 苗书立, 杨建宇, 熊金涛. 12b双通道高速A/D转换器AD9238的原理及应用[J]. 现代电子技术, 2004(13):1-4.

- 【22】 赵负图主. 信号采集与处理集成电路手册[M]. 北京市: 化学工业出版社, 2002.

- 【23】 黎玉刚, 张英敏, 付强文. 双口RAM在组合导航系统中的应用[J]. 电子技术应用, 2005(9).

- 【24】 王志鹏, 付丽琴. 可编程逻辑器件开发技术MAX+plus II[M]. 北京市: 国防工业出版社, 2005.

- 【25】 吴宝丽, 陈健. 基于FIFO与电平转换器的DSP高速ADC系统[J]. 国外电子元器件, 2004(10):25-28.

- 【26】 祁煜, 李启炎, 翁良科, 等. 基于CPLD和FIFO的多通道高速数据采集系统的研究[J]. 电子工程师, 2003(2):44-47.

- 【27】 罗林根, 曾奕, 李立学, 等. 基于CPLD和AD9248的高速采集系统的设计与实现[J]. 工业控制计算机, 2008(2):15-87.

- 【28】 黄建才. 基于ARM技术的大气激光信号处理技术研究[D]. 长春: 长春理工大学, 2008.

- [29] ANALOG DEVICES INC. Low Distortion Differential ADC Driver AD8138[EB/OL]. http://www.analog.com.

- [30] ANALOG DEVICES INC. 14-Bit,20MSPS/40MSPS/65MSPS Dual A/D Converter AD9248[EB/OL], http://www.analog.com.

- [31] CORPORATION . MAX7000 Programmable Logic Device Family[EB/OL]. www.altera.com.

- [32] INTEGRATED DEVICE TECHNOLOGY INC. 3.3VOLT HIGH-DENSITY SUPERSYNC II<sup>TM</sup> NARROW BUS FIFO[EB/OL]. www.idt.com.

- 【33】 张洪健. 基于ARM的电池极板涂布厚度在线测控系统研究[D]. 哈尔滨工业大学, 2009.

- 【34】 刘晓萍. 基于ARM的换热站数据采集与控制系统研究[D]. 哈尔滨工业大学, 2009.

- 【35】 姚磊. 基于ARM的间接炉气式木材干燥窑监控系统设计[D]. 西北农林科技大学, 2009.

- 【36】 宋子敬. 基于ARM的力觉接口设备控制系统的研制[D]. 哈尔滨工业大学, 2008.

- 【37】 李乐星, 基于ARM的喷浆机器人控制系统研究与设计[D]. 山东科技大学, 2009.

- 【38】 井利民, 基于ARM的苹果图像果实识别与定位关键技术研究[D]. 西北农林科技大学, 2009.

- 【39】 李妍. 基于ARM的汽车行驶记录仪研究及应用[D]. 武汉理工大学, 2009.

- 【40】 肖永生. 基于ARM的嵌入式开发平台设计[D]. 哈尔滨工业大学, 2008.

- 【41】 浦昭邦, 赵辉主. 光电测试技术[M]. 北京市: 机械工业出版社, 2009.

- 【42】 王树本主编. 高频电子线路原理[M]. 1998.

- 【43】 刘君. 大气温度及气溶胶激光雷达探测技术研究[D]. 西安理工大学, 2008.

- 【44】 黄春行. 超高速数据采集系统的时序设计与信号完整性分析[D]. 南京理工大学, 2004.

- 【45】 姚嘉, 施旭霞. CPLD在超高速数据采集系统中的应用[J]. 电子技术应用, 1998(10).

- 【46】 宋志强、余红英、CPLD控制ADC0809实现多路数据采集[J]. 黑龙江科技信息, 2009(33):66.

- 【47】 李晓琴. 2GSPS数字存储示波器数据采集控制与数据处理软件设计[D]. 成都: 电子科技大学, 2008.

- 【48】 张天佑, 激光雷达数据的高精度高速采集及可视化的研究[D]. 西安理工大学, 2009.

# 附录 A

- A-1: AD 采样部分原理图

- A-2: CPLD 部分原理图

- A-3: ARM 核心控制图

- A-4: ARM 外围器件原理图

## 附录B

```

模块名称: AD-FIFO 控制模块。

模块功能:控制 AD 采样,及控制采样数据存入 FIFO。

输入端口: SCLK-- 模块时钟输入。(20M)

RSET-- 模块复位信号,复位后需重新使能,上升沿开始工作,高有效。

EN -- 使能信号,上升沿开始工作,低有效。

END -- 采样结束信号,上升沿开始工作,低有效。

输出端口: AD OE-AD9248 输出使能信号,使能输出低电平有效。

AD CLK EN-AD9248 时钟使能信号,使能输出低电平有效。

FIFO_CLK_EN-- FIFO 时钟使能信号,使能输出低电平有效。

module AD FIFO(SCLK,RES,EN,END,OTR,BEFF,AD OE,REN,AD CLK EN,FIFO CLK EN):

parameter [1:0] state START=2'b00,state WAITING=2'b01,state COUNTING=2'b10,state END=2'b11;

input RES;

input SCLK:

input EN;

input END;

input OTR;

output BEFF;

output AD OE;

output REN;

output AD CLK EN;

output FIFO CLK EN;

reg BEFF;

reg AD OE;

reg REN;

reg AD CLK EN;

reg FIFO CLK EN;

reg star flag;

reg otr_flag;

reg [3:0] counter;

reg [1:0] STATE;

always@(posedge SCLK)

begin

if(RES == 1'b1)

//复位,开始标志置零

begin

STATE <= state START;

//状态机为初始状态

```

```

star flag <= 1'b0;

end

//模块使能

else if(EN == 1'b1)

begin

//开始标志置'1'

star flag <= 1'b1;

end

if(OTR = 1'b0)

begin

BEFF <= 1'b0;

if(otr_flag == 1'b1)

begin

otr flag <= 1'b0;

star flag <= 1'b1;

end

end

//模块开始工作

if(star flag == 1'b1)

begin

if(OTR = 1'b1)

begin

otr_flag <= 1'b1;

BEFF <= 1'b1;

//AD9248 输出禁能

AD OE \leftarrow 1'b0;

REN \leq 1'b0;

//AD9248 时钟禁能

AD CLK EN \leftarrow 1'b0;

//FIFO 时钟禁能

FIFO CLK EN <= 1'b0;

//状态机为初始状态

STATE <= state START;

//开始标志置零

star_flag <= 1'b0;

end

else

begin

case(STATE)

//'state_START' 状态, 初始化各端口

state_START:

begin

//计数器清零

counter <= 4'h0;

//AD9248 输出禁能

AD_OE \leq 1'b0;

REN <= 1'b0;

//AD9248 时钟禁能

AD CLK EN \leftarrow 1'b0;

//FIFO 时钟禁能

FIFO CLK_EN <= 1'b0;

STATE <= state WAITING;

end

//ˈstate WAITING'状态,等待 AD9248 转化延时

state_WAITING:

begin

```

```

//延时结束

if(counter == 4'h6)

begin

//计数器清零

counter <= 4'h0;

//AD9248 输出使能

AD OE \leq 1'b1;

REN <= 1'b1;

//AD9248 时钟使能

AD CLK EN <= 1'b1;

//FIFO 时钟使能

FIFO CLK EN <= 1'b1;

STATE <= state COUNTING;

end

//延时未结束,继续延时

else

begin

counter <= counter+4'h1;

STATE <= state WAITING;

end

end

//ˈstate COUNTING'状态,等待采

state_COUNTING:

样结束

begin

//采样结束

if(END == 1'b1)

begin

//AD9248 输出禁能

AD OE \leq 1'b0;

REN \leq 1'b0;

//AD9248 时钟禁能

AD CLK EN \leftarrow 1'b0;

//FIFO 时钟禁能

FIFO CLK_EN <= 1'b0;

STATE<=state_END;

end

//采样未结束,等待采样结束

else

begin

STATE <= state COUNTING;

end

end

//采样未结束,开始标志置零

state END:

begin

//状态机为初始状态

STATE <= state_START;

//开始标志置零

star flag <= 1'b0;

end

endcase

end

end

end

endmodule

```

# 攻读硕士期间发表的论文

- 1、**闫庆**, 华灯鑫, 周智荣, 李大成. 基于 ARM 的激光雷达高速数据采集系统设计 [C]. 2010 年西安理工大学研究生学术年会论文集, 2010, 11.

- 2、王玉峰,**闫庆**, 汪丽等. 西安地区水汽、湿度和气溶胶的拉曼激光雷达观测[C]. 第一届中国激光雷达学术会议. 2010, 11.

- 3. LiWang, YufengWang, QingYan. Abstracts of papers[C].International symposium on Atmospheric Light Scattering and Remote Sensing (ISALSaRS09) July 13-17,2009, Xi'an